打造IC人才

科技生态圈

打造IC人才

科技生态圈

发布时间:2022-08-01

来源:IC修真院

一、绪论

今天周杰伦的新专辑发布。虽然我喜欢听朴树和许巍,但还是等到了现在,大概是莫名奇妙的仪式感,毕竟现在已经很少有人认真拍MV了。

我们来介绍后端设计相关的内容。说句题外话,这篇文章中的图我从学生时代实验室的师兄祖传的一个PPT中摘录的(Synopsys IC Compiler的一个toturial,还有部分图摘自网络,侵删),刚开始学习这个要的就是胆大。。。

由于当时实验室还没有点开后端外包这个科技点,后端都是我们自己做的,于是靠着这个PPT自己瞎弄出来的芯片dummy没加,DRC都没清干净就直接给台积电签了个责任书丢出去tape out了,最后竟然芯片还能跑。有时候还有点怀念那时候可以瞎搞的日子。

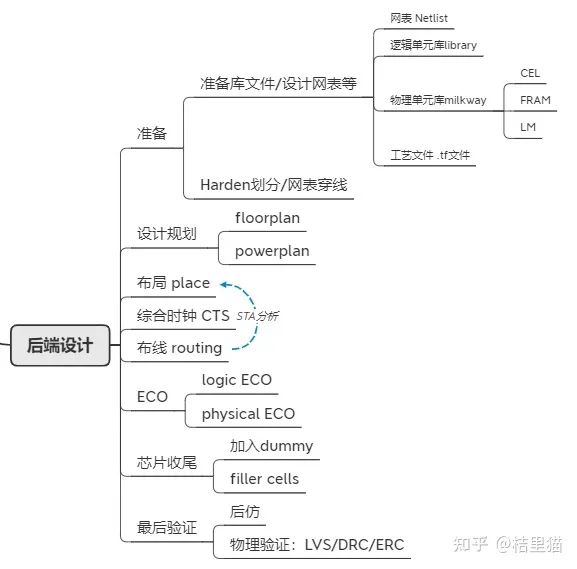

言归正传,后端主要解决的问题是怎么把网表制作成台积电等代工厂。我们还是按照步骤介绍,每个步骤都能单独写一篇文章,此处先介绍最基本的东西。

二、 STEP 0 准备工作

后端要启动起来其实要准备若干文件。需要干三件事儿。

1 准备网表\库文件

此处主要涉及1个网表,2个库,1个工艺文件。除了网表,其他都是台积电给的。

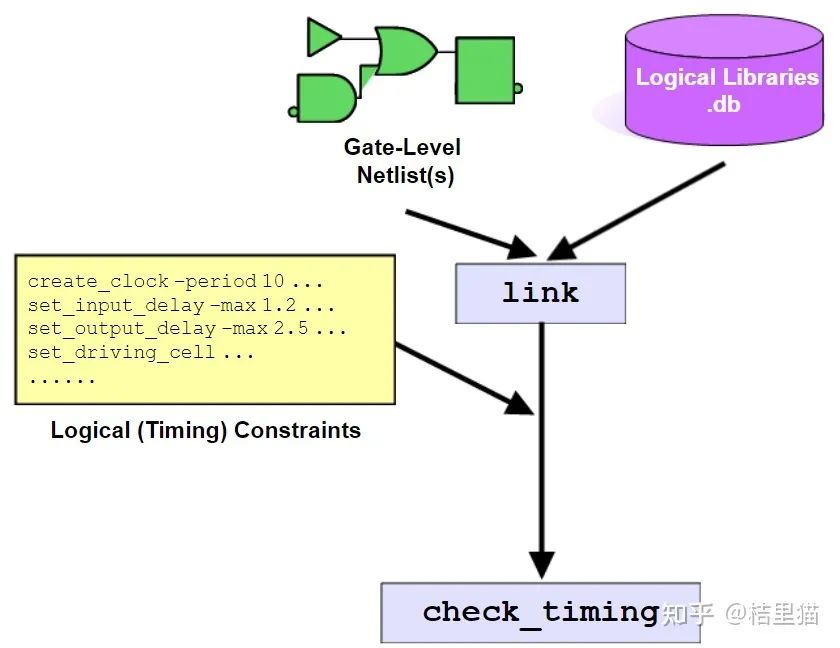

网表由前端设计的DC生成。相关内容不熟悉看(三—1)前段设计中的内容。

库文件主要是两个,一个是logic libraries, 主要带逻辑单元比如与门的setup, hold等等,后端需要检查这些时序信息从而完成后续步骤。

另一个比较重要的库就是物理库milkyway,主要包含了标准单元的物理信息。如下图所示,milkway主要包含了三种内容。CEL文件夹下都是版图信息,标准单元库有多大,pin在什么位置上。FRAM是版图的一个缩略版,主要是用来布局布线时用的。LM其实是logic model的缩写,由于我们前面已经有了logic libraires,这个LM此处不一定有,有了也不一定用。

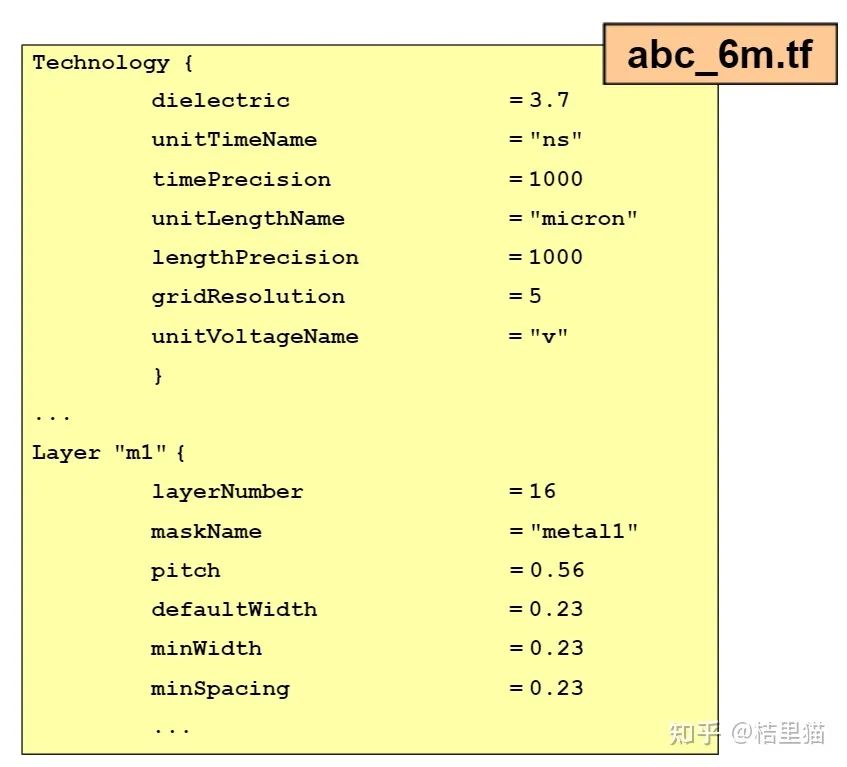

工艺文件.tf文件。这个主要是包含了工艺有几层金属,金属线能有多接近等DRC规则,当然还有ICC看版图时各层的颜色等等。与制造相关的信息基本在这个文件里。文件里的内容大致上如下图。

2 Harden划分、网表穿线

按理说,这个地方应该在DC前就划分好的,此处就拿到这个地方讲了,因为和后端关系比较紧密。由于现在芯片系统越来越复杂了,如果把所有东西放在一个网表里做,DC时间和布局布线时间根本不可能接受,所以其实都是分块做,然后再拼起来的。怎么分harden是个技术活,大致就是要求harden之间的连线尽量少。因为harden之间的连线后期不是靠工具,而是靠工程师手动连上的。

划分好harden,还有个网表穿线问题。。这个问题是偶然向NVIDIA后端团队跳出来的一个牛人请教时知道的, 这个哥们原来在NVNDIA做显卡的后端,20系列和30系列显卡应该都有参与,然后觉得后端工作太过重复不太有挑战性,人间不值得,于是跳槽做前端设计了。

为什么要穿线?因为有时候做后端的时候会有下图这种问题。

如上图所示,hadren A和harden C之间是有连线的。但物理实现的时候可能要求harden A和harden C在芯片上不挨着放。这个时候只能在harden B的网表上传个线,把harden A和harden C连起来。据传说,这个东西有经验的工程师可以手动添加。

这个步骤完了,我们的准备工作就完成了,可以动手设计版图了。

三、 STEP 1 设计规划

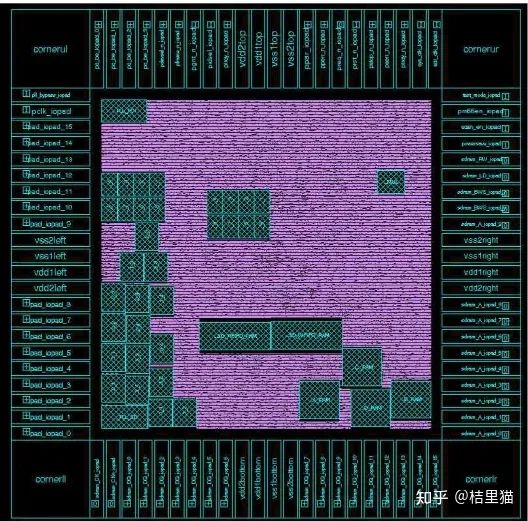

设计规划里主要做的是两个步骤。第一个是floor plan,第二个是power plan。过了这个步骤,芯片的面积就确定下来了,IO的位置也确定下来了。可以设计PCB板子了。设计规划大部分工作都是手动完成的,属于后端中工作量非常大的一块内容。后面布线虽然耗时长,但需要工程师深度参与的反倒不多。

floor plan 这个步骤主要是固定一些大块的东西,这些东西工具是没法自动给你摆放到一个比较好的位置的。

如上图所示,你要指定各个RAM到底放在芯片版图的哪个位置,哪些位置可以给工具放标准单元,哪些位置是IO, IO PAD位置也确定下来。这个步骤其实讲究还蛮多,需要前端设计人员和后端设计人员共同来完成。

比如RAM要想办法摆在芯片的四周(你可以想想,为什么RAM要摆在芯片四周)。与IO有链接关系的模块也要尽量和IO近,方向要朝着IO。内部交互线比较多的模块要摆在一起。另外,有些IP线很多,需要在周围留一圈空间用来布线,否则可能布不通。

power plan 有人会把这个步骤放在floor plan中,但是此处把它分开了。因为这个步骤工作量挺大,还容易出错。这个步骤主要是把电源网络给铺好,这个电源网络要满足IR drop, 各处要供电均匀。此处实在是没有找到一个power。

大致描述一下,芯片内部供电其实就是一个网络状的供电网络,周围一圈联通的叫power ring, 中间一条一条的电源线叫power strip, 标准单元库就连接在这些strip上。一般喜欢放在顶层金属,因为顶层金属比较厚。我见过所有电源网络都是手动敲代码布置的,似乎也有可以自动用工具来做的。总之就是,电源网络要保证各处能联通,尤其是SRAM不要出问题,然后各处IR drop,EM电迁移不要出问题。

这一步结束后得到下面的版图,只是把东西都摆上去了。还没有连起来。周围一圈是pad, 中间是RAM和标准单元。

四、STEP 2 Placement 布局

此处开始放置标准单元。由于有了上一个步骤的规划,这个步骤放置的标准单元其实是自动的。工具会自动把标准单元按算法就近的摆在一起。这个步骤应该好理解。

如上图所示,把相关的单元摆放在一起,同时要根据扇入扇出换用合适的单元。摆放的太密线布不通,摆放的太松浪费芯片面积。总之,这一个步骤人为参与的很少,主要是工具自己来摆放,因为单元实在是太多了。

今天有人提了个问题,为什么每次布局布线结果都不一样。主要是工具为了加速收敛,采用了大量的启发式算法,比如常用的模拟退火算法就在这个地方大量使用,感兴趣可以查查启发式算法。

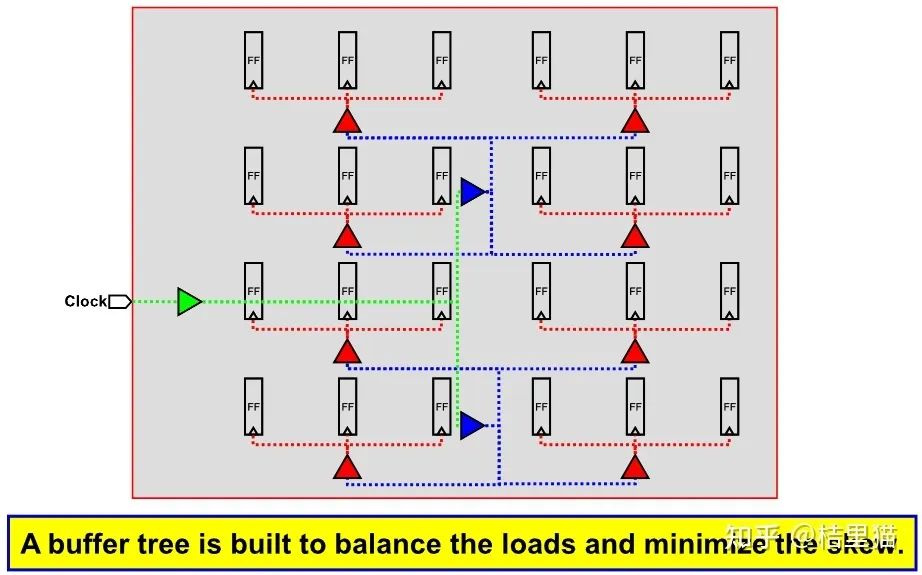

五、STEP 3 Clock Tree Synthesis

经过上个步骤,我们已经把标准单元都放好了,这个步骤我们就是把时钟网络摆好,这个步骤基本上也是由工具做的。如下图,生成一个H形状的时钟网络。

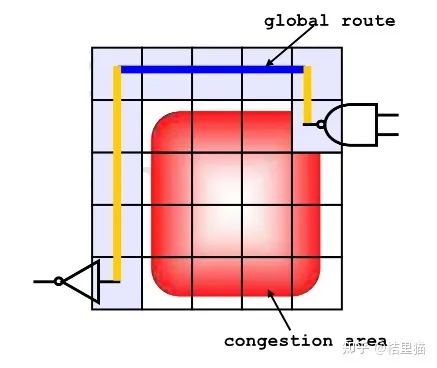

六、STEP 4 Routing

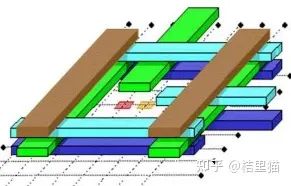

这个步骤主要是把线联通。。。此处我们最先要搞清楚一个问题,芯片里面的线不是一个平面连接的。

而是向上图一样,有多个层,每个层只走固定方向的线(横的或者竖的),层之间靠打孔连起来。Routing做的就是把相关单元的连线通过这些线连起来。

如图,把与门与反相器连起来。打两个孔,用三段线就能连起来。需要注意的是,这个步骤结束以后,要进行STA分析(静态时序分析),看看各个器件的setup, hold时序是不是都能过,不能过,从布局那步开始迭代,直到所有时序通过了。实际的工具布线会有好几轮,global route, detail route, 直到所有布线都连通,而且基本没有DRC错误。

七、STEP 5 ECO

ECO全称是engineer changing order。主要存在两种ECO, logic ECO。这种常见于设计错误。。。UT,IT,ST统统没有发现问题,等要流片前发现了个BUG。。。这个时候就要启动ECO流程,一般大家肯定是不希望有logic ECO的,但实际上芯片项目一大,每次都会ECO出现。

这个时候就需要有人背锅。physical ECO是另一种ECO, 主要是修一些工具搞不定的timing, DRC错误等,这些东西比较常见,工具的算法不够只能导致的,不属于错误,但也需要人为修改掉。

八、STEP 6 芯片收尾

收尾阶段主要加入dummy,filler cells等。主要目的芯片加工的时候刻蚀的时候线密度太低或者逻辑单元密度太低会影响良率,所以在没有连接线和没有放置单元的地方放一些无用的金属和基本单元。

九、STEP 7 最后验证

在芯片最后交版图之前,还要做最后的检查。主要涉及到LVS, DRC,ERC检查以及后仿,还有一些其他的检查,此处就先不展开讲了, 最终目的是让版图不出什么错。

后仿是最后做成版图以后提取的网表以及延时sdf文件,仿真看看时序是不是有问题。这一步理论上来讲如果上面步骤里setup hold都修干净了此处不会有问题。不过一般还是不会省略这一步。

LVS 主要是检查一下,芯片版图联通的是和网表要求的一致的。LVS是Layour Versus Schematics的缩写。原理就是通过版图提取一张网表,和原来的网表对应一下,如果有问题报出来。大部分情况不会出问题,都属于虚惊一场,但还是有出问题的时候,比如电源地没连对什么的问题。

DRC 是design rule check的缩写。检查一下版图中画的东西都能不能造出来。比如线宽太细了,再比如说线按的太近了,都要在这一个步骤报出来。一般来讲,总会有DRC错误。DRC错误都是要修掉的,实在修不掉要和代工厂确认。如果代工厂认为有危险,仍然要下单要给代工厂承诺芯片出问题了代工厂不负责。

ERC检查芯片的电气特性。Electrical Rule Checking。主要检查类似于MOS的gate是不是接了supply, 衬底是不是悬空了这些问题。一般应该不会出问题。

十、总结

这篇文章主要介绍了后端的大致流程。后端东西也比较多,可能每个小方向都能单独写一篇文章。但总之,这个阶段的输入是前端设计的网表(netlist),输出是给代工厂用于加工的版图(GDSII)。至此,设计就完全结束了。后面就该加工制造了。

相关推荐

下一篇:如何成为一名合格的芯片设计工程师

推荐阅读

2023-06-08

2023-02-01

2022-12-14

2023-03-07

2022-09-23