打造IC人才

科技生态圈

打造IC人才

科技生态圈

发布时间:2023-03-23

来源:IC修真院

SPI是Serial Peripheral Interface的简称,是由Motorola公司推出的一种高速、全双工的总线协议,可以实现一对一、一对多芯片通信。

SPI接口信号

SPI由SCLK、CS/SSEL、MOSI,MISO四根线组成,

SCLK,时钟信号,时钟频率即SPI速率,和SPI模式有关;

MOSI,主机输出,从机输入;

MISO,主机输入,从机输出;

CS/SSEL,从机设备选择,低电平有效;

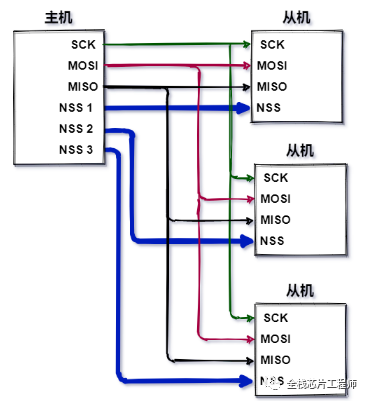

多从机模式

如果主机有多个片选CS端口,可采用下图模式,主机只能获取一个从机的MISO信号,其它从机输出信号须为高阻。

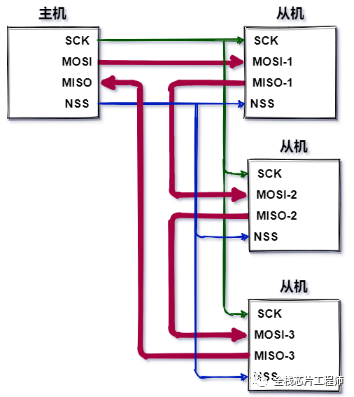

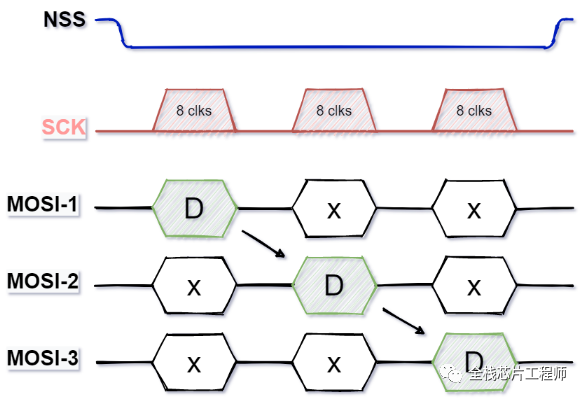

菊花链连接,节省GPIO、节省布线面积,但需要保证从机支持菊花链模式。

菊花链的数据传输时序:通过移位 送达数据。

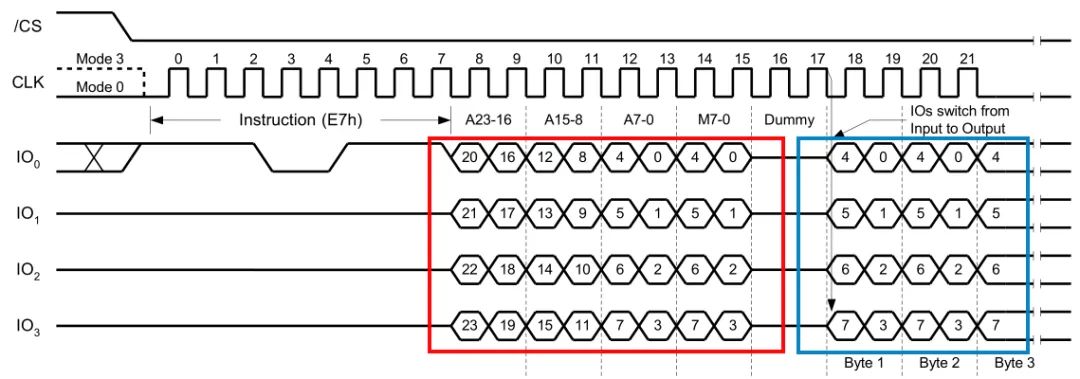

QSPI协议

QSPI协议读写时序:

注意,很多人写公众号都没说清楚,为什么SPI能做到全双工,而有些QSPI不能呢?

因为从下面时序图可看到,发送时,待发送数据的一组8bit寄存器只在下降沿向左移位(高位先发,低位补充0即可),那么必然存在另一组8bit寄存器用以在上升沿接收数据,这样就可以构成全双工,而QSPI一般用FIFO/SRAM进行数据传输,基于成本考虑,一般只能半双工。

SPI工作模式

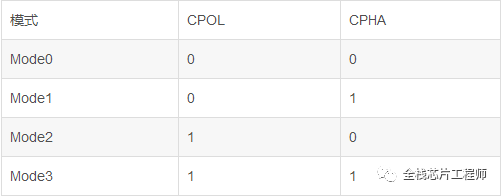

根据时钟极性CPOL(Clock Polarity)、时钟相位CPHA(Clock Phase),SPI有4种模式,最广泛使用的是模式0和3:

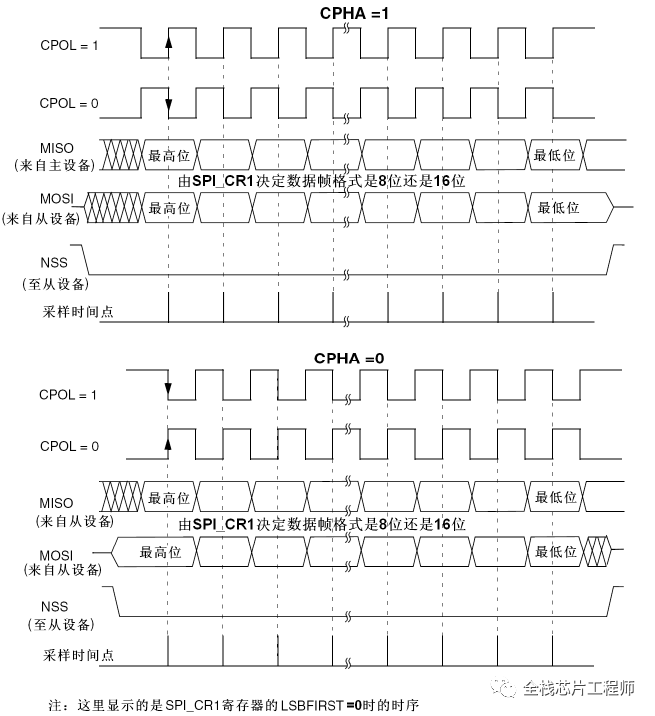

官方时序图如下:

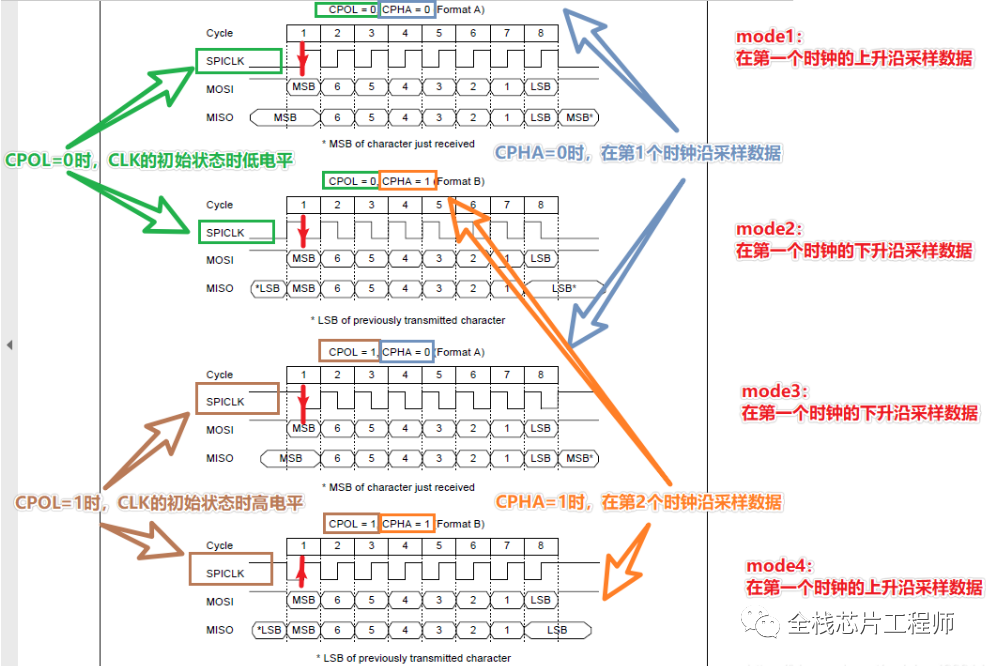

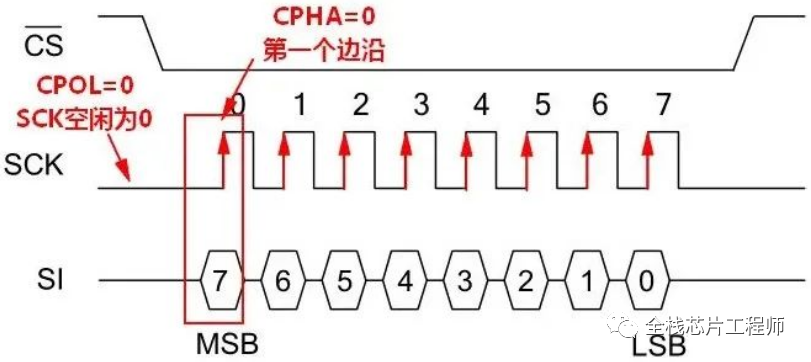

CPOL=0 CPHA=0(常用)

CPOL=0,SPICLK空闲状态为低电平;

CPHA=0,SPICLK第一个边沿(上升沿)采集数据、第二个沿输出数据;

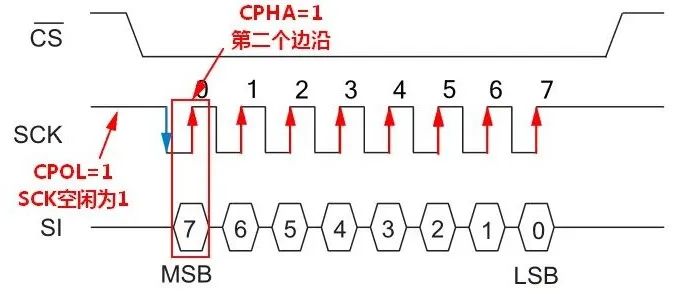

CPOL=1, CPHA=1 (常用)

CPOL=1,SPICLK空闲状态为高电平;

CPHA=1,SPICLK第二个边沿(上升沿)采集数据、第三个沿输出数据;

CPOL=0,CPHA=1 (不常用)

CPOL=0,SPICLK空闲状态为低电平;

CPHA=1,SPICLK第二个边沿(下升沿)采集数据、第三个沿输出数据;

CPOL=1,CPHA=0

(不常用)

CPOL=1,SPICLK空闲状态为高电平;

CPHA=0,SPICLK第一个边沿(下升沿)采集数据、第二个沿输出数据;

相关推荐:

推荐阅读

2022-08-02

2022-09-08

2022-09-27

2023-05-29

2022-06-02