打造IC人才

科技生态圈

打造IC人才

科技生态圈

发布时间:2023-06-08

来源:IC修真院

随之而来的是秋招了,各位ICer你们有没有准备好面试呢?今天给大家准备了“2023数字IC设计笔试题—燧原”希望能对从事IC设计的同学有所帮助。

一、单选|5分

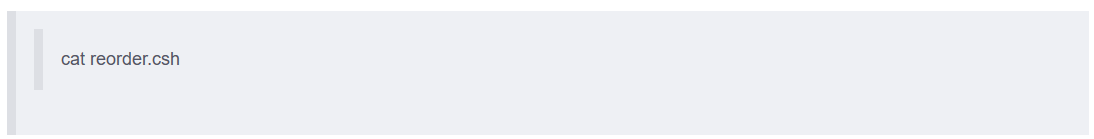

1、在terminal中输入命令得到如下结果:

输入如下命令并敲下回车后,可以得到哪种输出?( )

A.reorder.csh is a 666 test

B.test 666 is a

C.test 666 is a reorder.csh this

D.666 a test this is

答案:C

解析*:

在执行 Shel 脚本时,向脚本传递参数,脚本内获取参数的格式为: Sn。n代表一个数字,0为执行的文件名(包含文件路径),1为执行脚本的第一个参数,2 为执行脚本的第二个参数,以此类推

$cba 即 $4 $5 $2 $3 $0 $1: test 666 is a reorder.csh this

2、高频放大器工作频率越高,以下说法正确的是( )

A.增益变大,带宽变小。

B.增益和带宽都小。

C.增益变小,带宽变大。

D.增益和带宽都大。

答案:C

解析*:

可参考:运放使用总结篇(5) 运放高频增益的制约因素

频率越高,结电容的容抗就越小,则结电容的旁路作用就越显著,晶体管的电流放大倍数β就越低,放大器的增益就越低。

放大器的电压增益AV越高,则等效的密勒电容越大。等效到基极的密勒电容将与前级电路的输出电阻构成一个RC低通网络,从而限制了放大器的带宽。

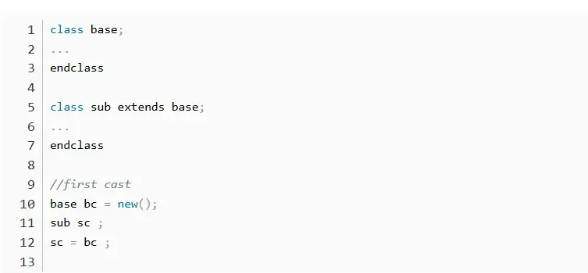

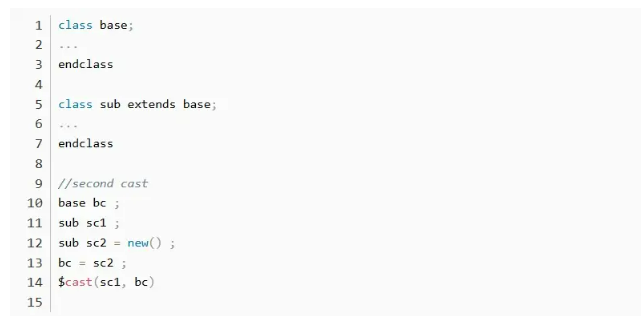

3、判断下面代码是否正确?

a.

b.

A.true true

B.false true

C.true false

D.false false

答案:B

解析*:

可参考:《2005 V: Verilog IEEE Std(1364-2005)》

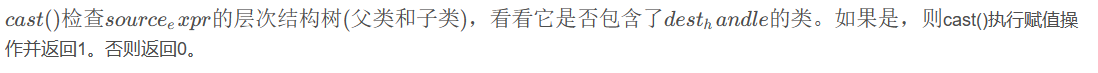

将子类变量赋值给继承树中更高级别类的变量总是合法的。直接将超类变量赋值给其子类的变量是不合法的。但是,如果父类句柄指向给定子类的对象,则将父类句柄赋给子类变量是合法的。

$cast( singular dest_handle, singular source_handle );

当与对象句柄一起使用时,

A 属于直接将父类变量赋值给其子类,不合法。

B 父类句柄bc指向子类对象sc2,然后将父类句柄指向子类变量,是合法的。

4、In ARM AMBA AHB protocol, which of fllow in responses is ONE cycle response?

A.RETRY

B.ERROR

C.SPLIT

D.ORAY

答案:D

解析*:

可参考: 《IHI0033C AMBAAHB协议标准》

两种传输响应: OKAY 和 ERROR

虽然OKAY响应可以在一个周期内给出,但ERROR响应需要两个周期。开始ERROR响应,下级驱动HRESP为HIGH表示ERROR,同时驱动HREADYOUT为LOW将传输延长一个额外的周期。在下一个周期中,HREADYOUT被动为HIGH,以结束传输,HRESP保特为HIGH,表示ERROR。

5、Which of the following metal layer has Maximum resistance?

A.Meta15

B.Meta13

C.Meta18

D.Meta12

答案:D

解析*:

后端布局布线的知识,金属数越小,drc宽度越小,电阻越高!

6、在对信号做降采样前添加滤波器,一般需要添加什么样的滤波器,完成什么功能:

A.低通,抗周期延拓

B.高通,抗混叠滤波

C.低通,抗混叠滤波

D.高通,抗周期延拓

答案:C

解析*:

可参考:《软件无线电原理与应用》

抽取D倍: 原始频谱展宽D倍。需要在抽取前滤除pi/D外的频率分量,达到抗混叠的效果。

内插l倍: 原始频谱压缩l倍。需要在压缩后滤除pi/i外的频率分量,达到抗周期延拓的效果。

7、Based on your understanding about the gray code and asynchronous FlFO design principle, the minimum asynchronous FIFO depth is ( )

A.4

B.2

C.4

D.1

答案:C

解析*:

假定,格雷码跨时钟域打了两拍,则为了保证读写地址同步这两拍数据不丢失,需要深度至少为4。

8、指令系统中程序控制类指令的功能是( )

A.实现算数和逻辑运算

B.实现程序执行顺序的改变

C.实现堆栈操作

D.实现主存于CPU 之间的数据传送

答案:B

9、以下选项中,不是Python中用于进行数据分析及可视化处理的第三方库是( )

A.Mxnet

B.mayavi2

C.numpy

D.Pandas

答案:A

解析*:

MXNet是一个深度学习框架

10、芯片的功耗和下面四个因素中哪个没有直接关系?( )

A.芯片的面积

B.时钟频率

C.工作温度

D.供电电压

答案:C

解析*:

CMOS 电路功耗类型:

动态功耗:负载电容充放电引起的功耗。

静态功耗:漏电流引起的功耗。

二、不定项选 7分

二、不定项选 7分

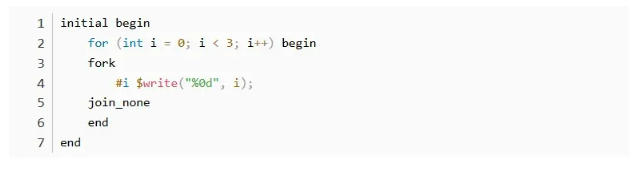

1、What' s the execution output of below code in verilog simulation?

A.333

B.012

C.iii

D.000

答案:A

解析*:

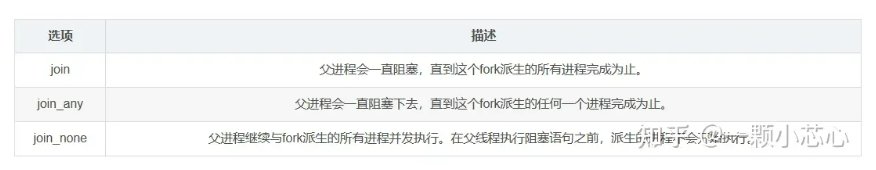

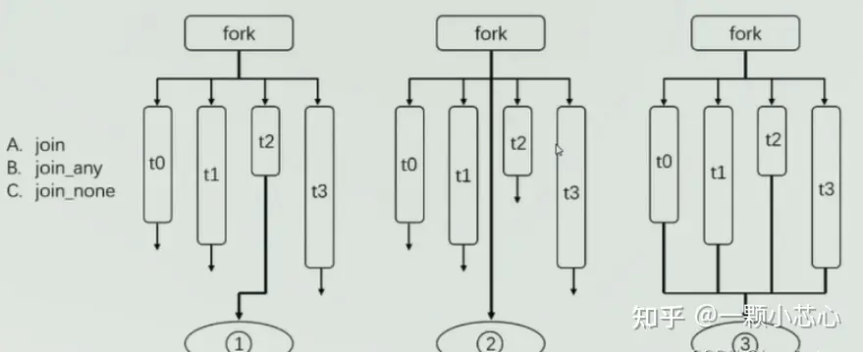

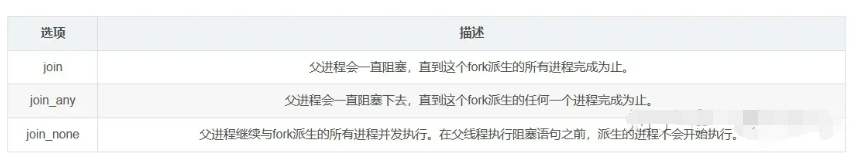

Fork...join 控制选项:

这里,三种语句对应的输出为

join: 0 1 2

join_any: 0 1 2

join none: 3 3 3

for语句执行完之后,fork派生的进程并发执行,此时i值为3.

2、Which can be used to convert std:string to char array std:string str = Hello world” -> char cstristr.size) + 1)(multiple answer)

A.cstr = (char *)str;

B.cstr = str;

C.memcpy(cstr, str.c_str(), str.size()+1) ;

D.strcpy(cstr, str.c_str()) ;

答案:C D

解析*:

string类型给char数组赋值.

A cstr = (char *)str.c_str();

未验证,答案仅供参考。

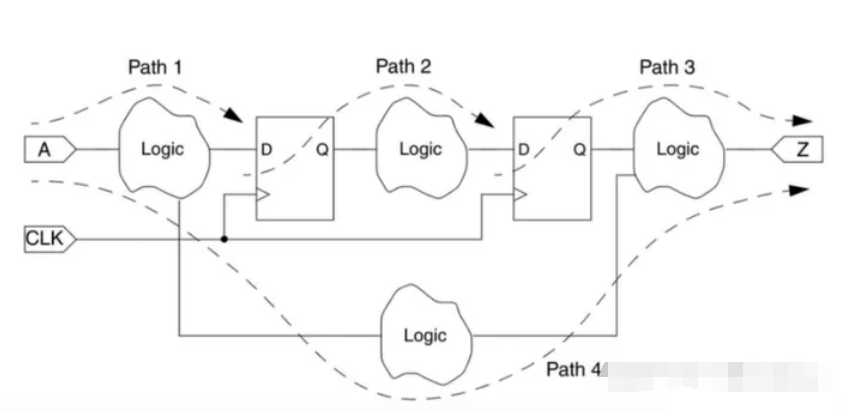

3、Which are correct start point candidates in STA for data path (multiple answer)?

A.clock pin of the flip-flop/latch/memory

B.input data port of design

C.Input enable port of clock-gating element

D.Set/Reset/Clear pin of the flip-flop/ latch/memory

E.output data port of design

F.data output Q pin of the flip- flop/ latch/memory

G.data input D pin of the flip- flop/1atch/memory

H.clock input port of design

答案:A B

解析*:

1.一个时序单元 (D触发器) 的时钟脚 (如path2)

2.输入端口 (如path1)

时序路径的终点

1.D触发器的D端

2.输出端口

4、Please select DFT processes which would normally be running in design-under-test silin

A.at high frequency

B.path delay fault test

C.MBIST test

D.netlist scan-insertion

E.ATPG pattern generation

F.IDDQ test

G.stuck-at-fault test

答案:B C D E F G

解析*:

参考《SOC设计方法与实现(第3版) 郭炜》第10可测性设计,其中是有提到固定型故(stuck-at-fault) 、传输延迟故障(pathdelay fault) 等。

5、We need to define clock specifications in SDC file,using commands like below:create clock -name CLK -period 600 waveform (0 3001.What can we know from this command?

A.Clock source latency.

B.KClock duty cycle.

C.Clock name.

D.Clock frequency.

答案:B C D

解析*:

-name选项: 时钟名称

-period选项: 周期

-waveform选项: 波形描述,包含占空比信息

6、Which statement(s) is/are correct

A.Toggle coverage reports describe design activity in terms of changes in signal value

B.Branch coverage is to describe coverage of all possible combination of conditions in every branch C.statementsAn FSM states' transition coverage is not a complete verification of the entire FSM modelCode

D. coverage can always reach 100% without any waive in RTL simulation

答案:A B C

解析*:

《SYSTEM VERILOG验证-测试平台编写指南》参考:

A: 翻转覆盖率(Toggle coverage)指示哪些单bit变量值为0或1B: 分支覆盖率(Branch coverage) 衡量代码中的分支覆盖的情况。if...else、case、?..:C: 有限状态机覆盖率(FSM coverage) 状态机中哪些状态和状态转换已经被访问过D:代码覆盖率

答案ABC不确定,仅供参考。

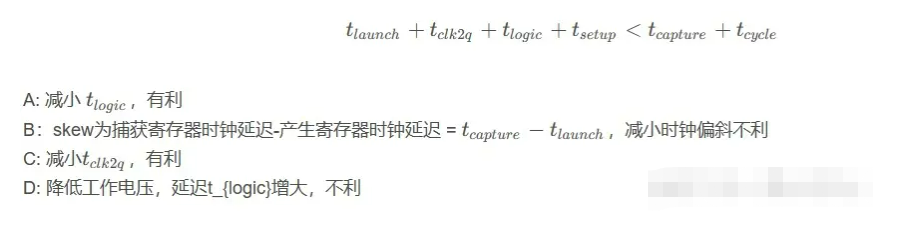

7、通常情况下,下列条件有利于满足Flip-Flop的建立时间的是:( )

A.将Flip-flop前的部分组合逻辑移到前一级Flip-flop前

B.降低时钟树上的skew

C.采用更先进的工艺

D.降低工作电压

答案:A C

解析*:

建立关系:

8、Cell Delay can be calculated based on:( )

8、Cell Delay can be calculated based on:( )

A.output transition.

B.input load.

C.output load.

D.input transition.

答案:C D

解析*:

参考:《Static Timing Analysis For Nanometer Designs》 3.2 Timing Modeling通过反相器的时序弧的延迟取决于两个因素

输出负载 (output load) ,反相器输出引脚处的电容负载

信号在输入端的过渡时间 (transition time)。

三、填空题|5分

1、在system verilog中,存在fork-join, fork-join any和fork-join none三种并行语句块的执行方式.下图展示了t0,t1,t2,t3四个并行语句块的不同执行方式,请据图从A,B,C三个选项中选择对应的选项填入D,2,处:

Fork...join 控制选项:

任意一个进程完成。join_any

任意一个进程完成。join_any

父进程与fork派生的进程并发执行。join none

所有进程完成。join

如果有其他朋友想要了解更多关于半导体/芯片/集成电路入行、就业等问题,欢迎互相交流学习也可以填写IC入行建议,来找IC工程师和你聊聊看。

另外,我们建了一个学习群,群内有一些共享的学习资料、IC行业资讯、设计和验证方面的项目,也有一些内推讯息。可以私信我:【加群】我们共享资源~

相关推荐:

相关推荐:

下一篇:嵌入式硬件工程师待遇如何呢?

推荐阅读

2023-03-03

2022-11-30

2022-10-21

2023-06-01

2022-11-16