打造IC人才

科技生态圈

打造IC人才

科技生态圈

发布时间:2022-12-14

来源:IC修真院

在《LYT-T002-V1.1 Cadence Virtuoso Layout 基本操作》文档中介绍了版图绘制软件 Virtuoso 的常规使用,其实对于一个软件的使用,快则几天,慢则几周就可以熟练的掌握,会使用软件不代表会版图设计,掌握一门技术的精髓在于基础理论知识的积累以及不断实践和寻找解决问题的途径,通过不断的经验积累最终形成自己独特的设计思维。本文档主要是从工艺和设计思维角度出发,用通俗的方式讲述了一些版图设计相关的基本理论,进而希望能开拓初学者模拟版图设计的思维。

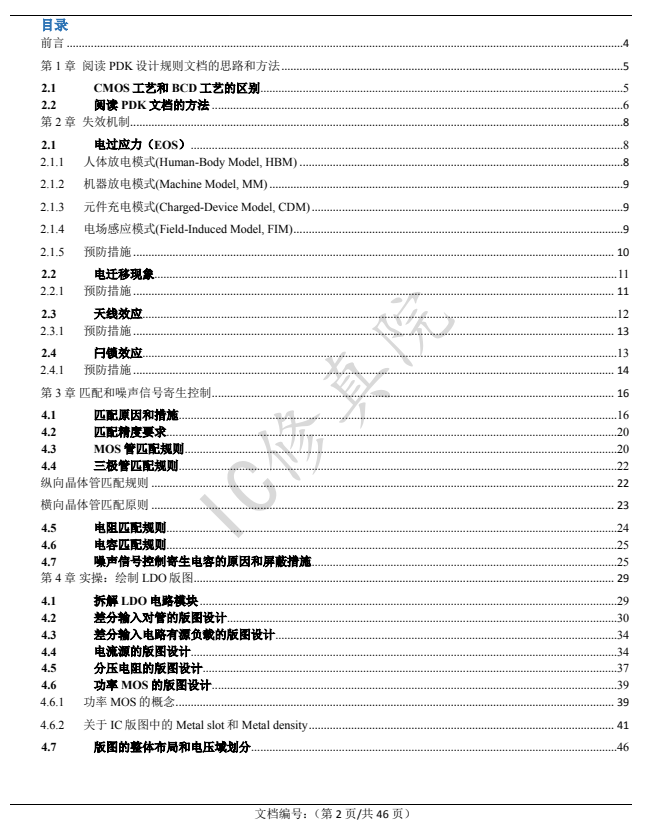

本文档第 1 章主要提供一种 PDK 设计文档的阅读思路;第 2 章主要讲述集成电路中的几种失效机制,包括电过应力、电迁移、天线效应、闩锁效应等,以及在版图设计上的的预防措施;第 3 章主要阐述了器件失配的原因,以及器件匹配的版图设计规则,并介绍了控制寄生电容的噪声信号的原因的屏蔽噪声信号的措施;第 4 章以 LDO 版图设计实例开头,重点讲解了功率 MOS 版图的版图设计方式以及相关理论。

本文档很多内容都来自于 Alan Hastings 著作《模拟电路版图设计的艺术》一书,只是有些内容按照个人理解进行了阐述且专业深度较浅。初学者在空闲之余可对该书进行详细阅读和钻研。

相关推荐:

立即下载

立即下载

推荐阅读

2022-12-22

2023-02-10

2022-11-09

2023-01-28

2023-02-08