打造IC人才

科技生态圈

打造IC人才

科技生态圈

发布时间:2023-01-12

来源:IC修真院

准备工作

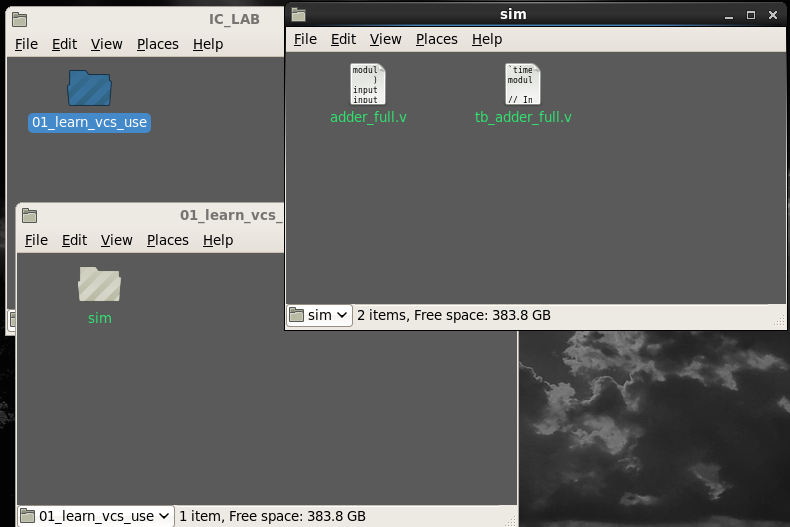

新建一个文件夹,将需要编译仿真的代码放到该文件夹内,这里在linux环境下创建了相关文件夹,并将全加器代码编写导入。

全加器代码:

module adder_full(dina,dinb,c,ci,dout

);

input dina;

input dinb;

input c;

output reg ci;

output reg dout;

always@(*)begin

{ci,dout}=dina+dinb+c;

end

endmodule

仿真代码:

module tb_adder_full();

// Inputs

reg dina;

reg dinb;

reg c;

// Outputs

wire ci;

wire dout;

// Instantiate the Unit Under Test (UUT)

adder_full(

.dina(dina),

.dinb(dinb),

.c(c),

.ci(ci),

.dout(dout)

);

initial begin

// Add stimulus here

dina=0;dinb=0;c=0;#10;

dina=0;dinb=0;c=1;#10;

dina=0;dinb=1;c=0;#10;

dina=0;dinb=1;c=1;#10;

dina=1;dinb=0;c=0;#10;

dina=1;dinb=0;c=1;#10;

dina=1;dinb=1;c=0;#10;

dina=1;dinb=1;c=1;#10;

end

endmodule

前仿真流程简述

这里提到的前仿真,我理解的应该属于是对模块功能的验证,这里对该部分加以概述。

根据实际的项目设计需求,提取相应的测试点,然后逐渐完善测试功能,完成测试环境的搭建,测试激励的产生**(Generate stimulus)工作完成后,将激励输入到待测设计(DUV - Design Under Verification)。将激励输入到待测设计后获取响应(Capture response),检查响应的正确性(Check the response for correctness)**然后根据验证目标评估验证进度。

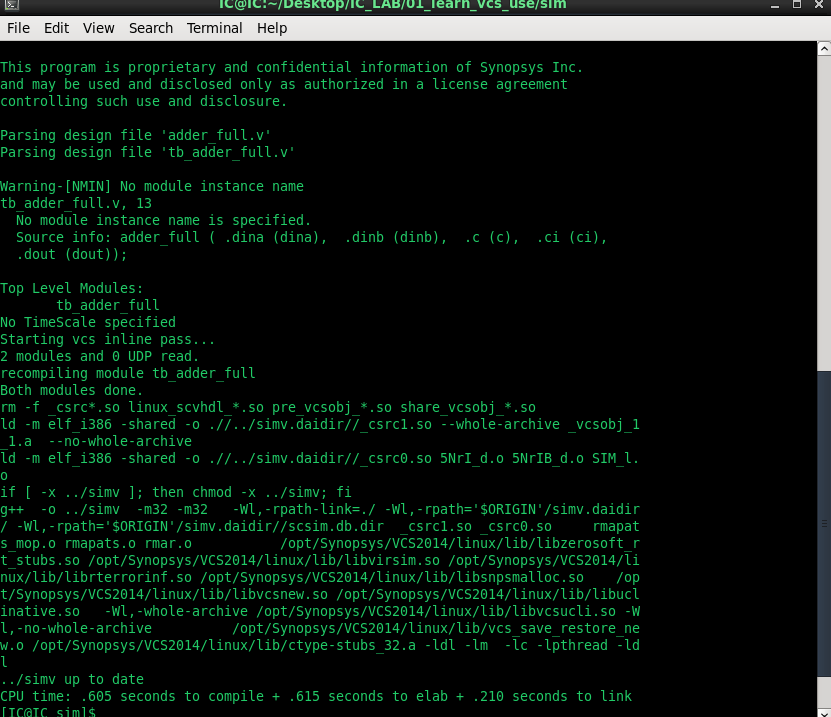

使用VCS编译代码

进入文件路径下然后在终端中输入以下命令:

vcs -sverilog -debug_all -timescale=1ns/10ps adder_full.v tb_adder_full.v -l com.log

vcs是逻辑仿真EDA工具的编译源代码的命令

-sverilog:编译命令选项,识别SystemVerilog语法

-debug_all:编译命令选项。可以将debug的信息全部保存下来,比如波形文件

-l com.log:编译命令选项,将编译过程生成的日志写入com.log文件

vcs编译完源代码,生成simv可执行文件。

vcs编译源代码时如果发现代码语法错误,会提出详细的error信息.

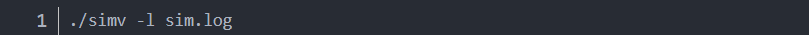

使用终端命令进行跑仿真(跑testcase)可以使用以下命令:

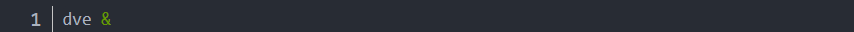

启动逻辑仿真工具VCS的图形化界面进行仿真

在终端中输入以下指令可打开VCS的图形化界面。

(&表示后台运行dve命令,不占用当前的terminal)

或者下述命令

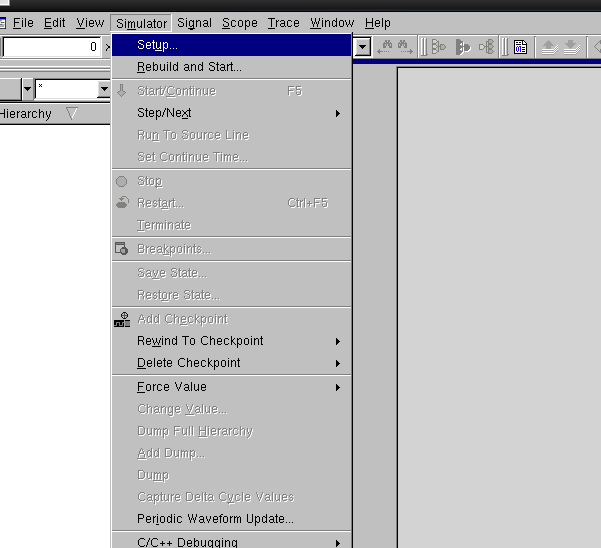

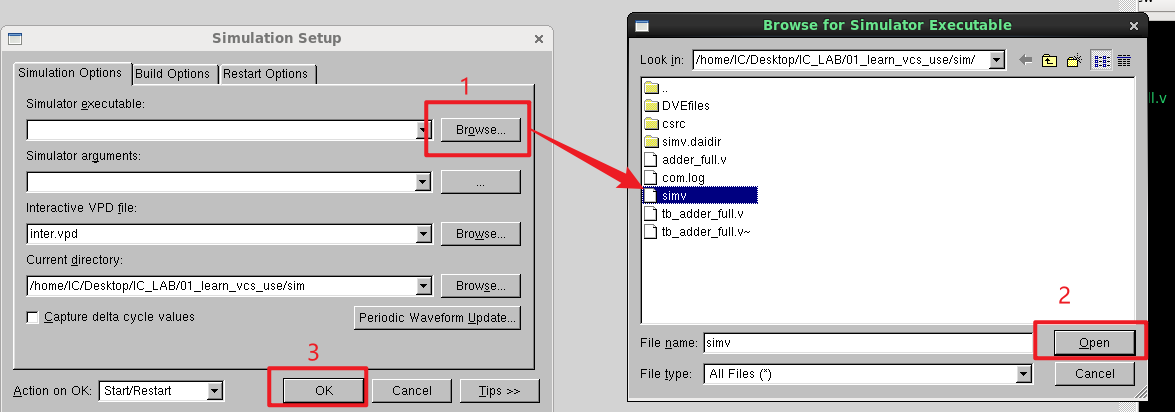

建立仿真,点击simulator下的setup,

添加simv文件,并打开。

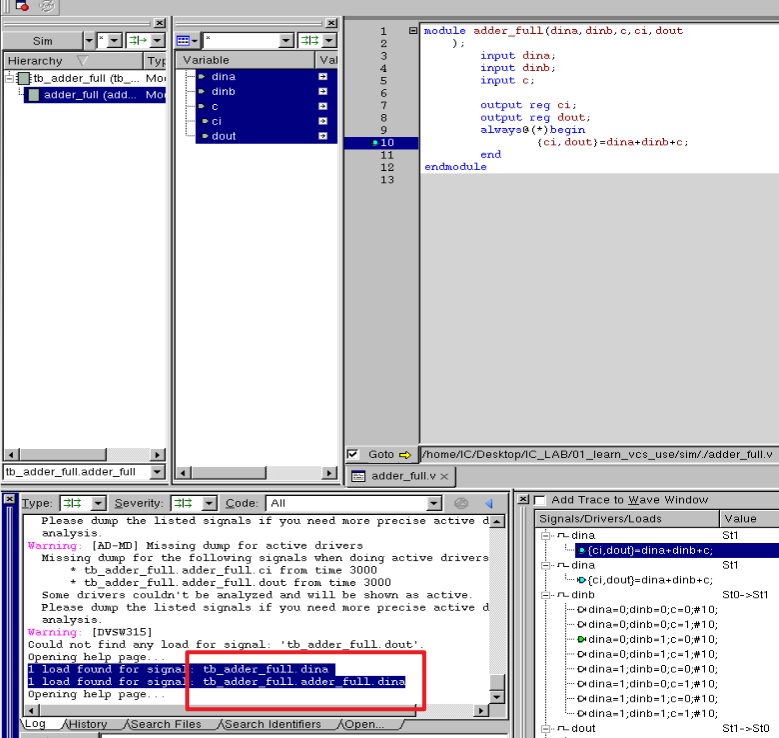

打开后界面如下:

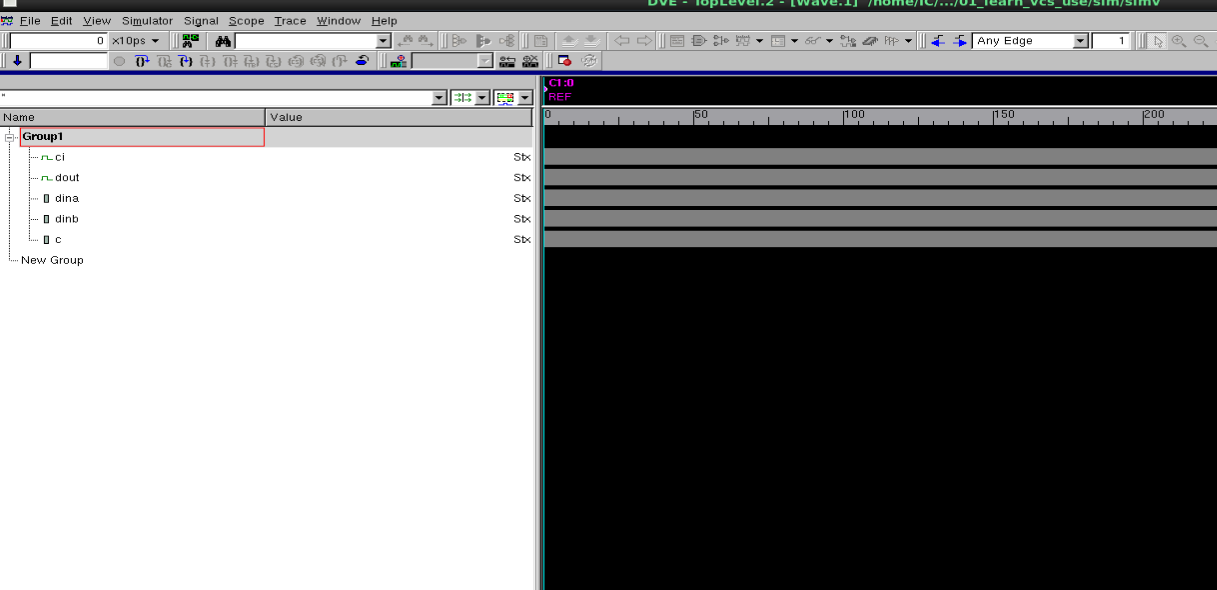

这个界面和questa sim或者modelsim的界面很像,在hierarchy界面中可以查看不同层级的信号变量,在variable里设置将这些信号添加波形到波形窗口中进行查看,按下图操作添加这些信号到波形窗口中。

点击添加到新波形窗口中界面如下,

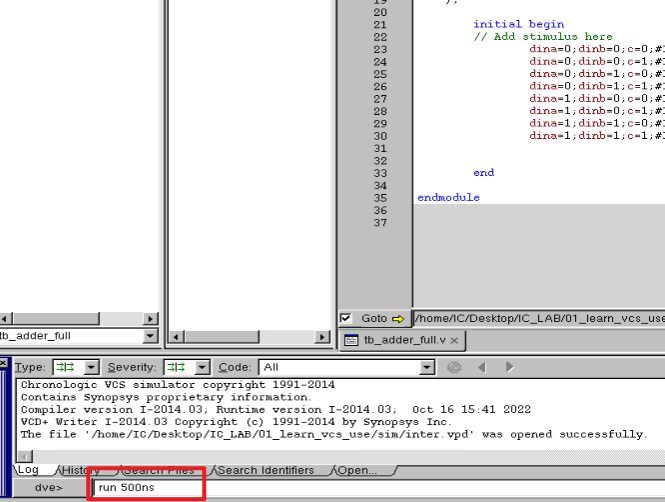

波形添加到界面中后,可以在dve的命令框中输入运行的时间执行仿真。

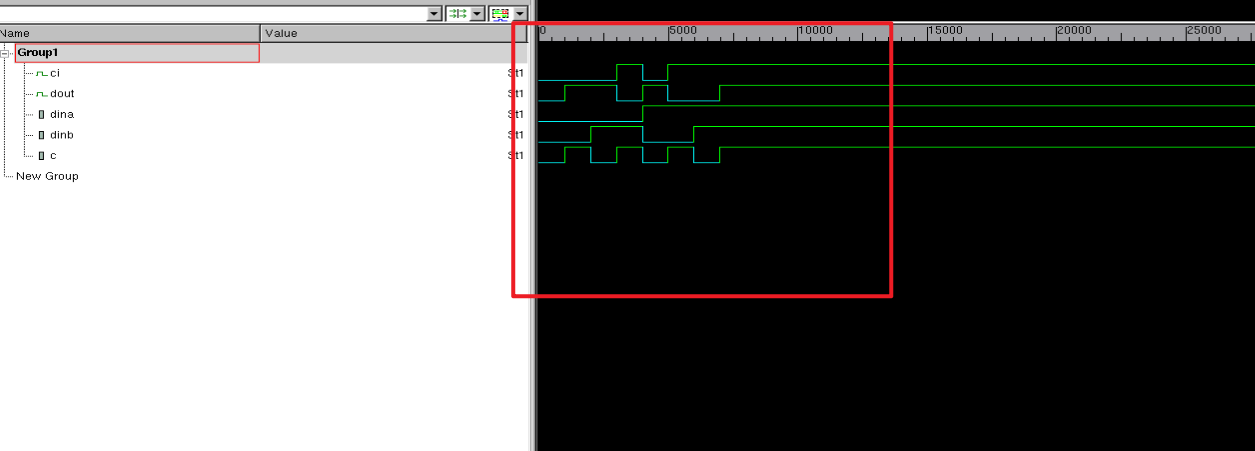

运行后切换至波形窗口可查看到仿真波形。

VCS的相关基本操作

本文只介绍目前我接触到的相关操作。

查看全部波形

在波形窗口中,单击f键会查看到全部波形,按住鼠标左键左右托取则会查看对应段的波形。

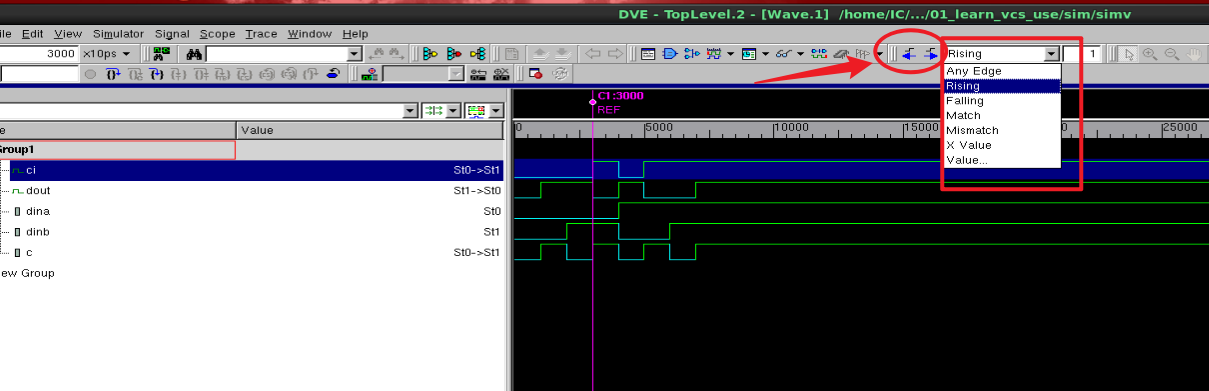

设置捕获

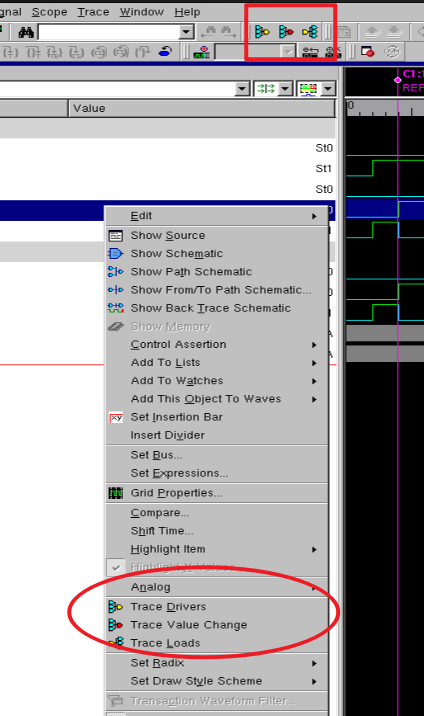

可以对信号的不同情况进行捕获,设置捕获的信号类型,然后圈选的可以查看上一个或者下一个该信号类型。

信号追踪功能

第一个:追踪驱动,快捷键: ctrl+d

第二个:追踪信号的值变换,快捷键: ctrl+shift+d

第三个:追踪负载,快捷键: ctrl+L

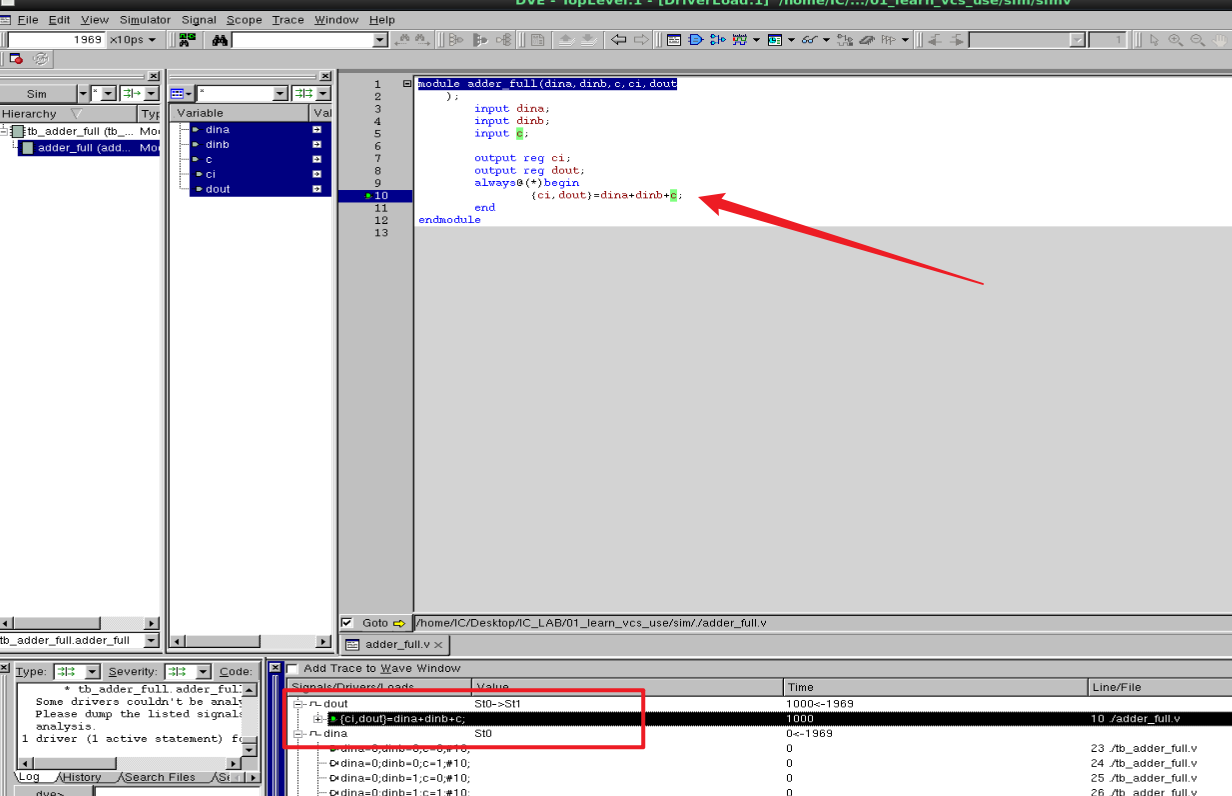

这里以dout为例,分析各个功能的效果。

这里追踪下dout的驱动信号,跳转对于了以下代码:

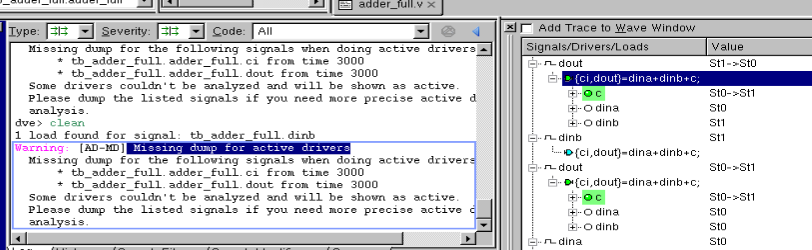

点击分析信号值改变时,这里报了warning,观察warning大致意思是,需要转存一下罗列的信号然后进行信号变化分析。

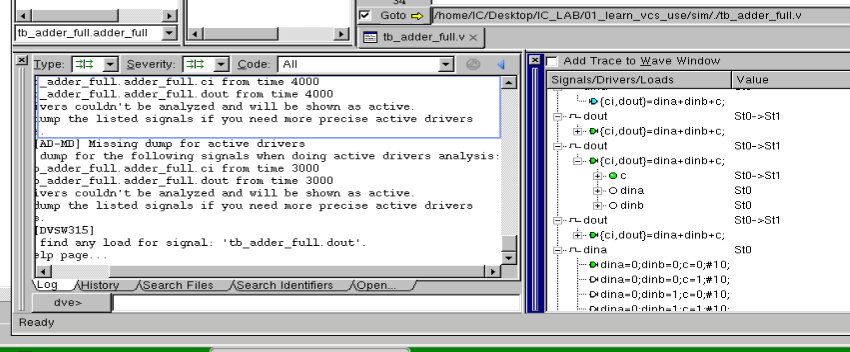

点击分析负载时,没有找到。因为在代码中dout不是任何信号的负载信号,所以这里无法找到dout的负载对应的代码。

如果对dina进行分析的话则可以找到相应的负载对应语句。

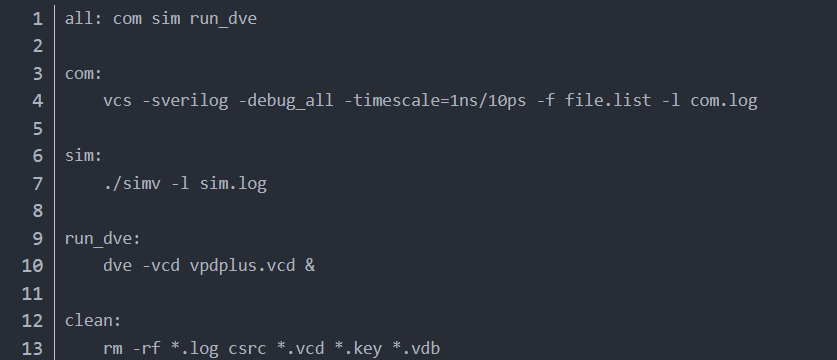

使用Makefile运行仿真

在linux环境中,vcd可以支持使用Makefile进行运行仿真,使用Makefile运行仿真可以极大提升工作效率。下面将整理一个Makefile脚本,以便于学习使用Makefile脚本进行仿真运行。

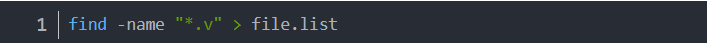

首先我们可以获取需要仿真的V文件的目录。

使用find命令在当前目录进行查找并生成list文件。

然后,新建Makefile文件,编写编译、仿真、运行dve和清除文件的脚本。

将上述的脚本保存,在需要仿真的终端中输入make XXX即可完成相应指令的工作,例如:make com,即可执行使用vcs进行编译的工作。

问题记录

I、llegal `timescale for module

解决:把v文件的timescale注释掉。在调用vcs中,加入参数:-timescale=1ns/10ps

相关推荐:

立即下载

立即下载

推荐阅读

2023-03-13

2023-03-23

2022-12-28

2022-05-23

2022-10-17