打造IC人才

科技生态圈

打造IC人才

科技生态圈

发布时间:2023-03-17

来源:IC修真院

1、数字后端的目的

数字前端设计:在集成电路设计中,从Verilog/VHDL代码(RTL级)编写验证再通过综合( synthesis)转换成门级网表( gate netlist)的过程。

数字后端设计(backend design):门级网表的物理实现,即把门级网表转换成版图。

完整的后端设计由后端半定制与后端全定制两个设计部分组成:

1)后端全定制设计是指在设计初期最先按照设计需求设计出的物理单元库,物理单元库由标准单元库、IP库及满足特殊需求的定制部件单元等组成。该物理库为后续后端半定制设计提供物理实现基础。

2)后端半定制设计是指使用布局布线工具并基于后端全定制阶段完成的标准单元库及IP库并根据前端设计完成整个芯片的组装与实现,这个过程又称为数字后端设计(自动布局布线-APR)。

传统上将布局布线前的工作称之为数字前端(Front End)设计,而将布局布线之后的工作称为数字后端(Back End)设计。

布局的目的在于产生制作掩膜所需的GDSII文件;同时也产生布局后的网表文件(Netlist)及标准延迟文件(SDF)。

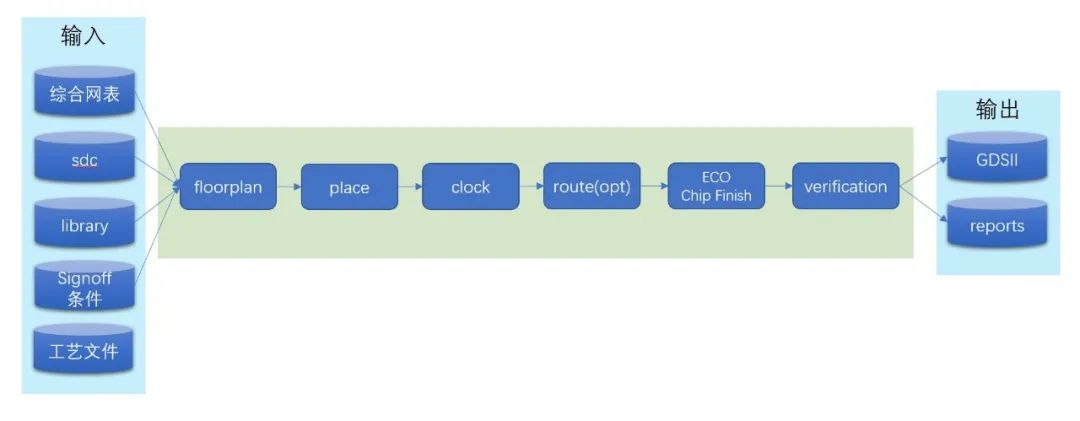

运用给定的输入,在给定的时间内做出符合signoff条件的PR结果并满足各种验证。

2、数字芯片后端工程师要做什么

主要工作就是接收数字前端提交的代码,最终交付一个完整的芯片布局布线结果。

工作职责:

(1) 从事SoC物理实现(P&R)工作,包括版图设计(floorplan)与后端验证(LVS/DRC)等

(2.)利用工具实现自动布局布线

3、使用的EDA工具

后端设计软件:

布局布线APR(Auto Placement &Route):Innovus/Encounter ,ICC2/ICC

综合工具:(带DFT)Synopsys DC,Genus

物理验证(PV):Mentor Calibre

静态时序分析(STA):Synopsys PrimeTime,Tempus

功耗分析(PA):Redhawk,Voltus,PTPX

仿真工具:Mentor modelsim/Questasim

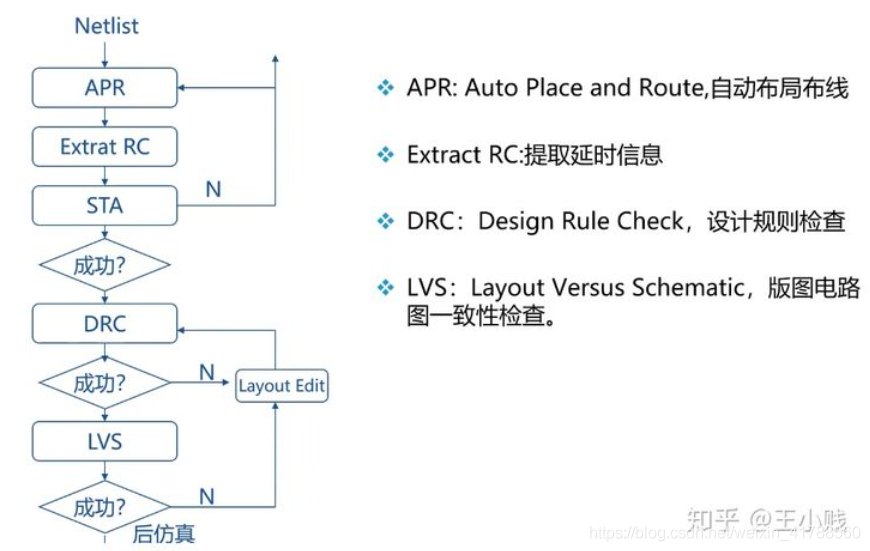

数字后端设计流程:

数字后端工作的开始——数据输入:

它包含了后端流程需要的所有文件:综合/DFT后的网表(netlist)、时序约束sdc、timing&physical等库文件、signoff的条件和设置以及各种EDA工具所需要的工艺文件。

Floorplan阶段

直接影响芯片的PPA(power, performance and area)

对整个设计进行一个宏观的规划,包括像模块大小的规划,Macro的摆放,电地power走线的规划。出pin的规划。decap的摆放,endcap的摆放,welltap的摆放等等。

Place阶段(或PlaceOpt)

主要内容是调用工具的算法对标准单元进行自动摆放。

对于网表中标准单元的摆放,根据优化的命令进行诸如插入buf,优化逻辑等等操作。旨在在设计初期,基于当前宏观floorplan 的规划下进行优化,进而可以看到工具导出的理想时钟树下的时序情况。

CTS阶段(Clock Tree Synthesis)

主要是时钟树的生长,基于设计约束中的关于时钟的定义约束进行时钟树的生成,在满足时钟drv约束的前提以及个人关于时钟约束的前提下生成树。

主要内容是根据floorplan和place的结果合理构建时钟树,并对有timing关系的clock进行balance。

Route阶段

包括布线后的优化,主要是调用PR工具的算法对design中的net进行自动布线,并在布线后继续优化timing, area和power等。

对设计中所有的单元进行信号线的连接。保证满足时序要求。同时会对绕线过程中的DRC进行修复工作。

最重要的就是能否绕通,也就是是否能够将绕线后的drc/short降至最低甚至0。

这部分routing的对象不包括power,analog等特殊net,因为这些net通常有特殊的约束,因此需要设计者根据工艺、floorplan以及其他constraint自行设计。

ECO阶段(Engineer Changing Order):主要是对于工具无法完全修掉的问题进行手动fix。

分类:

Logic ECO:对网表的逻辑功能的修改。

原因在于在芯片设计的后期阶段,前端工程师可能会发先设计上的某些bug而需要对电路做修改,而此时的schedule已经不允许进行重新综合,因此会选择在PR的网表上进行逻辑修改,一般情况是会增加一些逻辑或者将某些逻辑的net重新连接。

Physical ECO:主要是针对PR工具无法完全fix的问题进行手动修正。一般包括Timing ECO,drc fix等。

Chip Finish Process阶段

主要是对PR基本完成的网表在进行流片前为量产、良率已经后期改版做一些优化和准备。

一般包括插入filler cells、insert metal fill、修复antenna,某些flow可能会选择在这个时机插入tap或者boundary cells。

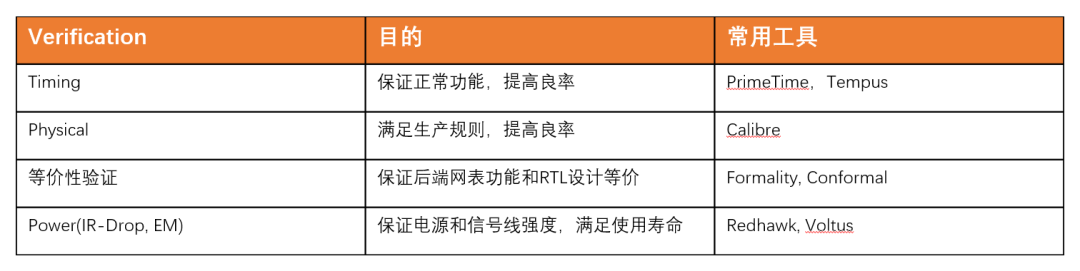

Verfication

验证,主要包括:

一切都没有问题之后,就可以signoff(或tapeout)。

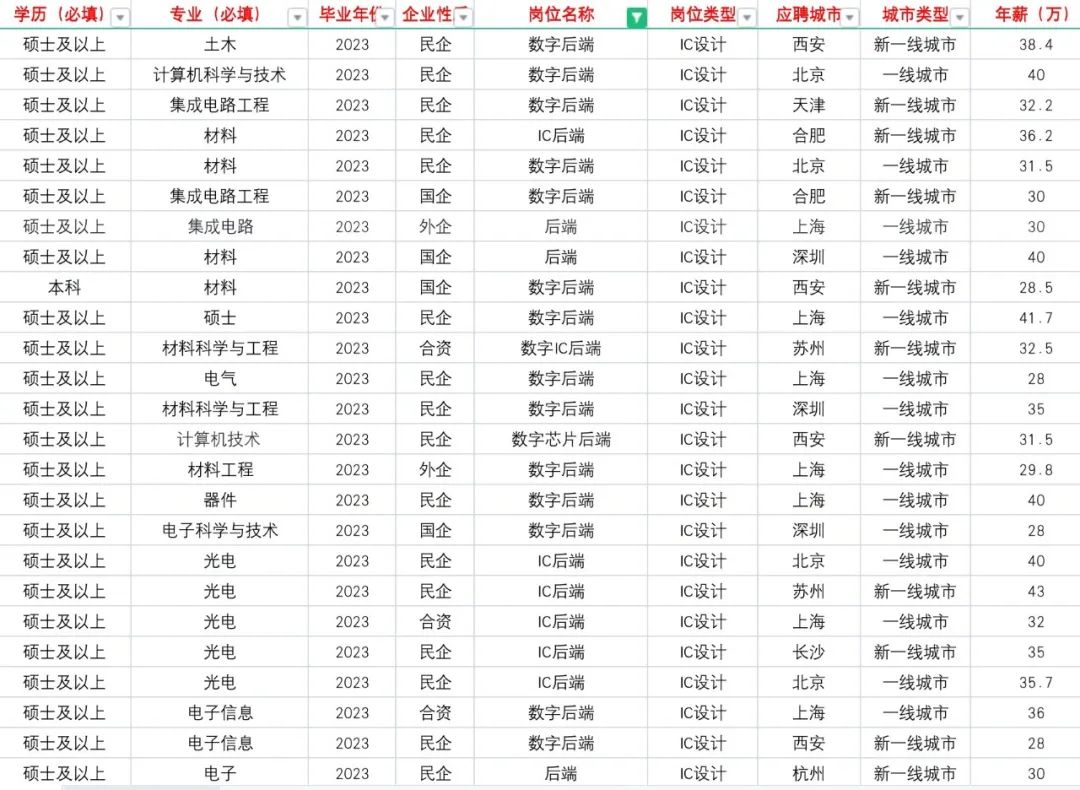

一般大一些的企业,数字后端设计各个模块都有明确的分工,每个人负责不同的设计模块,然后作为一个团队合作完成项目。数字后端工程师的薪资目前已达到较高水平:

现在更有一个学习数字后端设计的绝佳机会,不仅可以从最基础的理论知识开始学起,还能进行实战训练,积累项目经验,IC修真院精选《数字后端设计工程师就业直通营》从理论到项目,一步步带你走进数字后端设计的行列。

相关推荐:

立即下载

立即下载

推荐阅读

2022-11-09

2023-04-23

2023-01-05

2023-04-27

2022-08-03