课程简介:

本课程以数字IC设计岗位为导向,以RTL编程实践为核心,以数字逻辑方针和逻辑综合为基础,及基于ARM的Soc设计实现为重点,培养满足企业需求的数字IC前端设计工程师。

适合人群:

本课程适合本科及以上学历,高等院校电子类相关专业的人群学习(如:电子信息、微电子、通讯、计算机等);点击咨询>> 你适合学芯片测试吗?

主讲老师:

Kevin老师:10年数字前端设计工作经验。曾就职于中兴微电子研究院专家级前端设计工程师......

Pual老师:15年数字设计、架构工作经验。曾就职于高通担任架构工程师......

BOB老师:10年数字前端设计和架构工作经验。曾就职于UMC担任数字设计高级工程师.......

实战派老师指路,不走弯路,助你学习核心技能,就业顺畅。更多老师>>

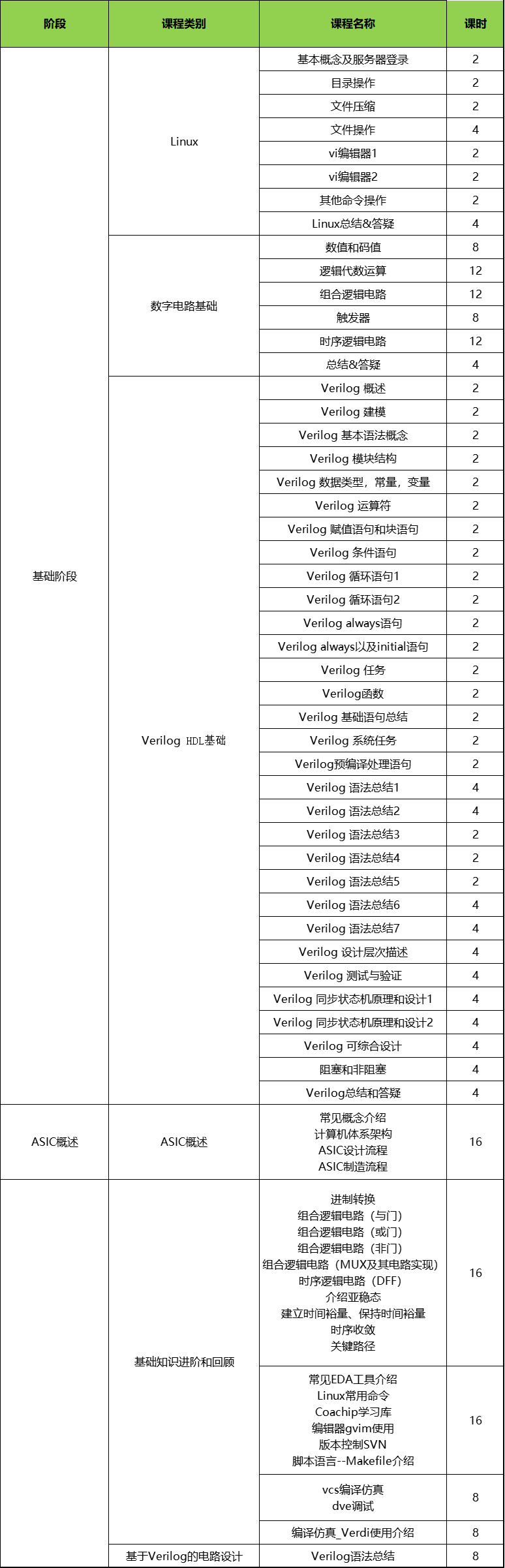

课程安排:

线上直播课+线下项目实训,上课时间为每周3次,每次2节课,24小时实时答疑;

项目实操:

项目名称:SoC芯片系统级设计

模块级项目:USB,CPU,MC,DMA,DDRC,12C, FLASH,SPI(选一)

项目类型:低功耗SoC芯片、商业级真实项目

项目工艺:28nm;

课程大纲:

就业薪资(参考):

平均薪资38W/年

初级工程师(25W - 60W)、中级工程师(45W - 80W)、高级工程师(60w - 100w)

就业介绍:

就业指导课+ 1对1就业服务 + 终身就业跟踪,随时提供就业服务。

1000余家企业招聘需求衔接、与大厂深度合作,定期为企业输送IC人才!

大家都在问: