课程简介:

本课程详细讲解数字集成电路后端实现的每个步骤:逻辑综合、布局、时钟树、布线、优化、ECO、GDSII,培养具备独立工程能力的数字IC后端工程师。

适合人群:

本课程适合本科及以上学历,理工科相关专业的人群学习(含材料、工艺、物理、自动化等专业);点击:咨询你适合学芯片后端吗? >>

主讲老师:

魏东老师:20年以上的数字IC后端经验,曾就职于英飞凌、航空航天研究所专家级数字后端工程师.......

小Y老师:10年后端设计经验,曾就职于三星半导体数字后端高级工程师.......

实战派老师指路,不走弯路,助你学习核心技能,就业顺畅。更多老师>>

课程安排:

线上直播课+线下项目实训,上课时间为每周3次,每次2节课,24小时实时答疑;

点击:了解详细的课程安排>>

项目实操:

项目名称:SoC芯片后端实现(低功耗SoC芯片)

模块级项目:MCU、AES(tsmc28)等;

项目特色:商业级真实项目

项目工艺:28nm;

点击:获取实战项目>>

就业薪资(参考):

平均薪资37W/年

初级工程师(20W-50W)、中级工程师(45W-80W)、高级工程师(60w-100w)

点击:查看以往学员就业案例>>

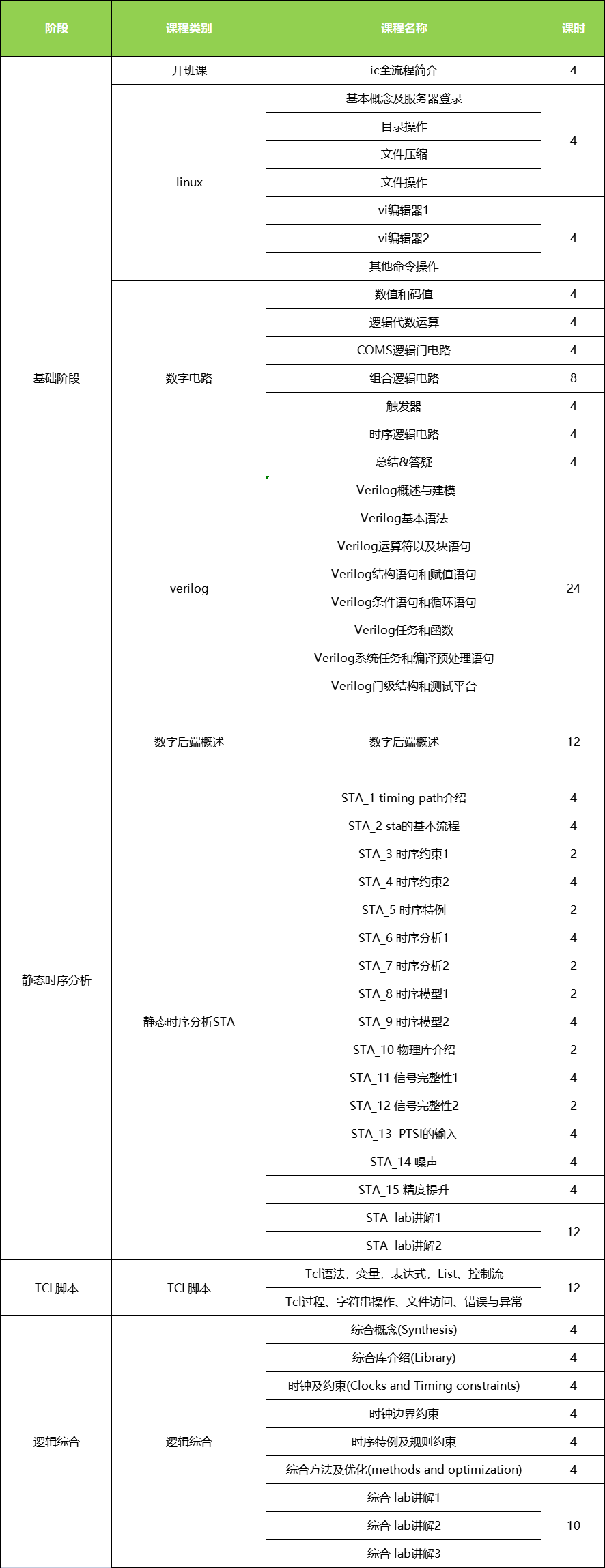

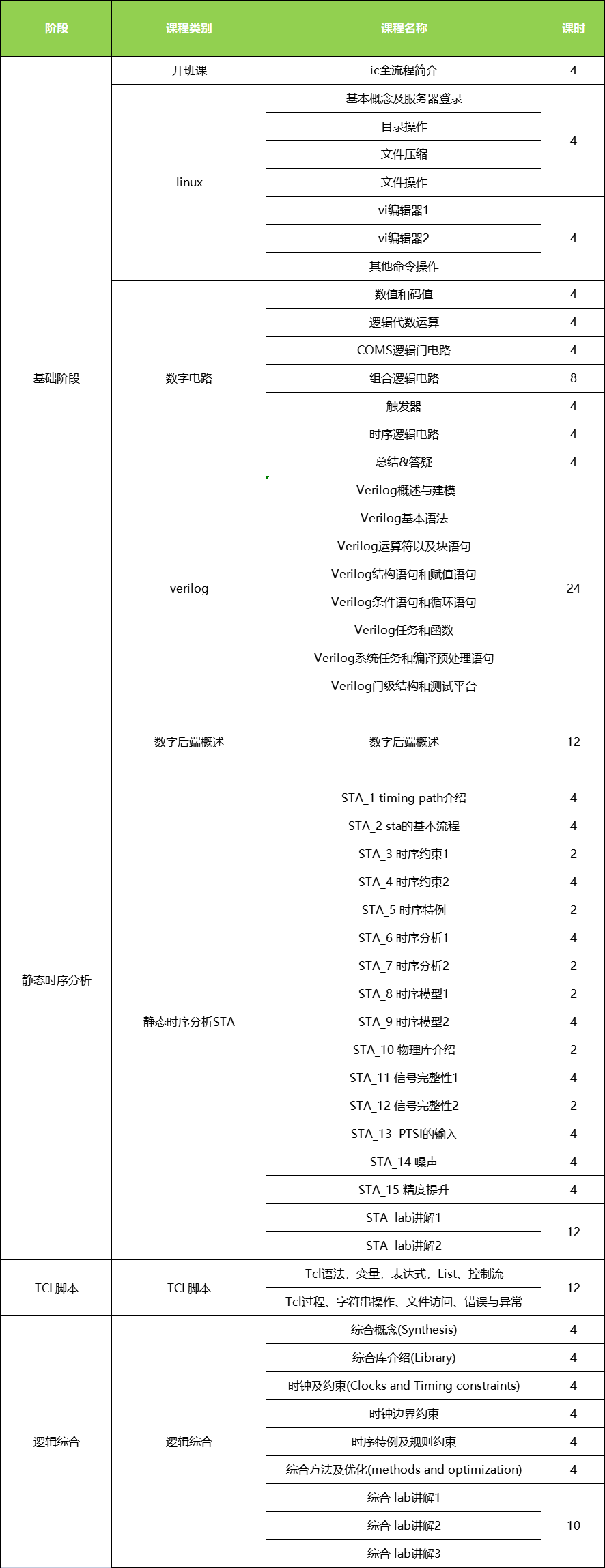

课程大纲:

点击:获取完整课程大纲>>

就业介绍:

就业指导课+1对1就业服务+终身就业跟踪,随时提供就业服务。

1000余家企业招聘需求衔接、与大厂深度合作,定期为企业输送IC人才!

点击:定制专属就业计划>>

大家都在问:

报名费用多少钱?

学习周期是多长时间?

零基础可以学会吗?

报名流程是怎么样的?

推荐免费课程

中国芯片业已经觉醒,并且正在不断进步,从国际、国内市场来看,我国集成电路产业市场前景广阔。在IC设计中,数字后端所占的人数比重一直是最多的,而且随着芯片规模不断加大,后端工程师需要的人数将会越来越多。资深数字后端工程师的薪资在50K-80K,所以对于IC行业科班出身或者想要转行的在职人来前景都是很明朗的。

职业简介:

数字后端处于数字IC设计流程的后端,属于数字IC设计类岗位的一种。数字后端按岗位类别可以分为:逻辑综合,布局布线physical design,静态时序分析(STA),功耗分析Power analysis,物理验证physical verification等岗位。

工作内容:

1.主要负责将RTL code转换为实际后端使用的netlist网表

2.布局布线(PD),负责netlist到GDSII的转化过程

3.静态时序分析(STA)

4.物理验证(PV)

5.功耗分析(PA)

6.熟练使用以下工具

8.布局布线:Innovus/Encounter, ICC2/ICC

9.综合:DC, Genus

10.物理验证:Calibre

11.静态时序分析: PrimeTime, Tempus

12.功耗分析: Redhawk, Voltus,PTPX

所需技能:

1.具有较好的综合知识,英语听说读写能力,团队合作,沟通能力,学习能力

2.有扎实的基础知识,数字电路、半导体工艺基础等

3.熟悉工具环境:LINUX,编辑器,EDA仿真工具

4.熟悉SoC从RTL到GDSII的完整设计流程

5.熟练综合技能及相关EDA工具使用

6.熟练自动布局布线技能及相关EDA工具使用

7.熟练时序分析 (STA)

8.熟练物理验证 (FV, PV, PA等)

适用人群:

有意应聘后端工程师的在职人员(统招本科及以上学历)

高等院校电子类在校研究生(含材料、工艺、物理、自动化等专业)