课程简介:

DFT设计工程师,是随着测试应运而生的一个岗位,是IC行业的多面手。目前在芯片设计中都离不开DFT。通过企业级真实案例由浅入深、由易入难,让学员熟练掌握企业级DFT。

适合人群:

本课程适合本科及以上学历,电子类相关专业的人群学习(如:电子信息、微电子、计算机等);

点击:你适合学DFT课程吗?

主讲老师:

星辰老师:20年以上数字ICDFT工程师,目前就任国内某研究所,担任专家级芯片DFT工程师.......

Jack老师:8年数字IC-DFT高级工程师,曾就职于国内一线大厂担任DFT研发高级工程师.......

实战派老师指路,不走弯路,助你学习核心技能,就业顺畅。更多老师>>

课程安排:

线上直播课+线下项目实训,上课时间为每周3次,每次2节课,24小时实时答疑;

点击:了解详细的上课安排>>

项目实操:

项目名称:MCU芯片

模块级项目:NPU

项目类型:商业级真实项目

项目工艺:65nm;

点击:获取实战项目详情>>

就业薪资(参考):

平均薪资36W/年

初级工程师(20W-50W)、中级工程师(45W-80W)、高级工程师(60w-100w)

以往学员就业案例>>

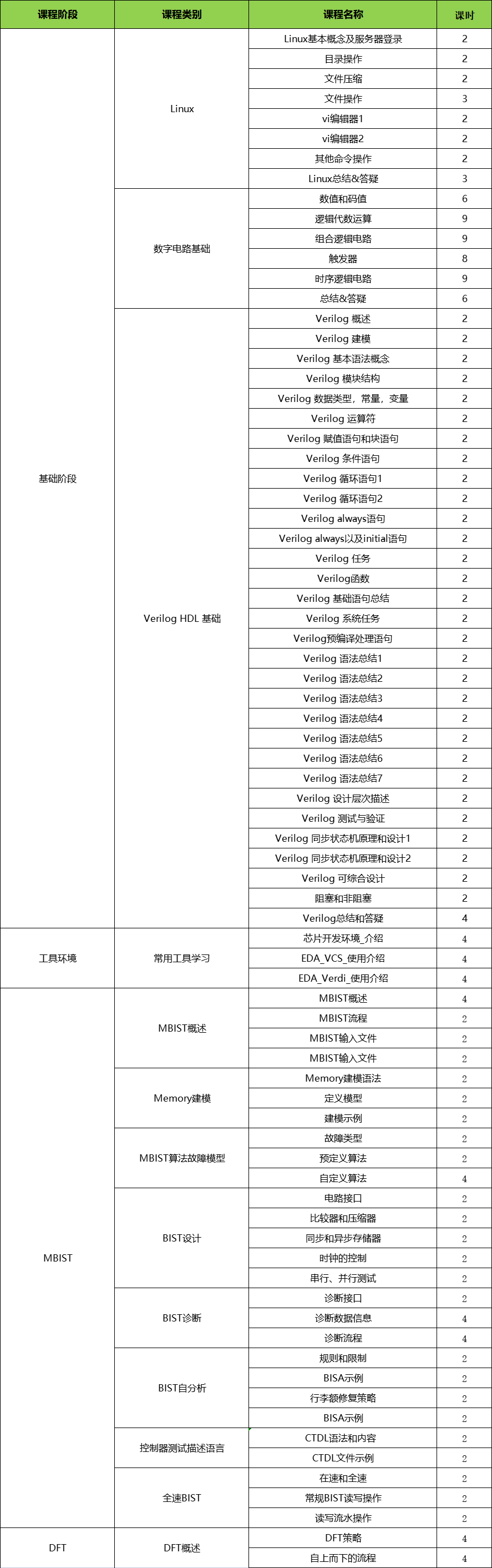

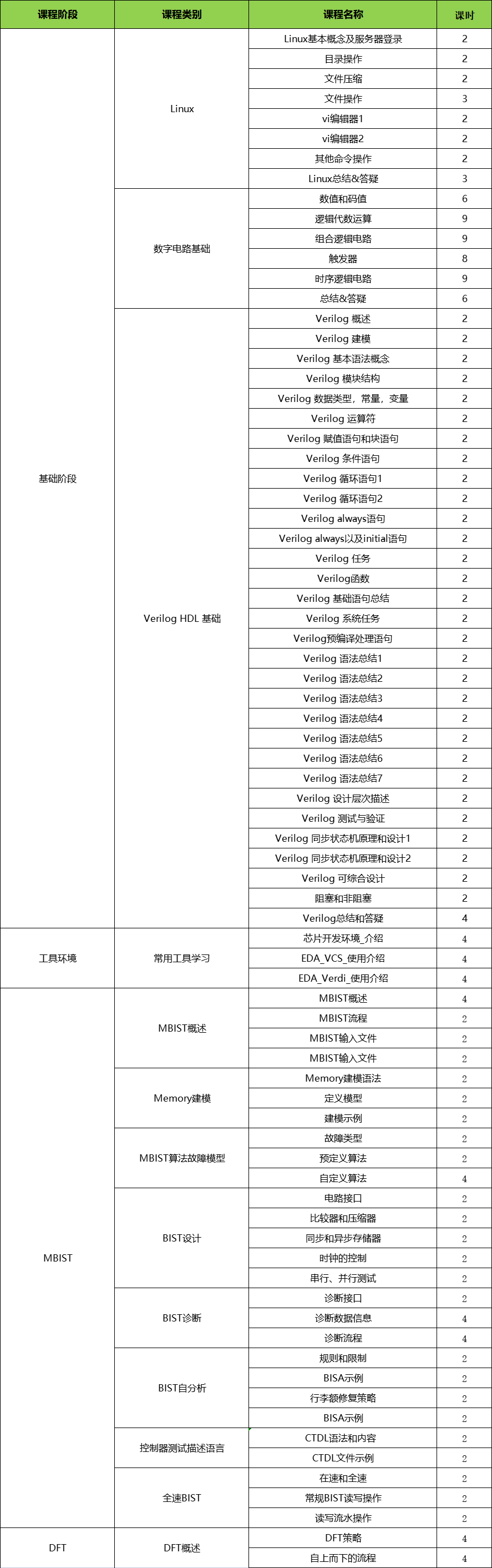

课程大纲:

点击:获取完整课程大纲>>

就业介绍:

就业指导课+1对1就业服务+终身就业跟踪,随时提供就业服务。

1000余家企业招聘需求衔接、与大厂深度合作,定期为企业输送IC人才!

点击:定制专属就业计划>>

大家都在问:

DFT报名费用多少钱?

学习周期是多长时间?

零基础可以学会吗?

报名流程是怎么样的?

推荐免费课程

DFT技术一直再进步,所以需要DFT工程师不停的学习和探索新技术,DFT可以有许多创新思想在里面,比如说设计公司自用的好的DFT模块,设计时钟和复位网络,调高测试覆盖率,debug ATE测试结果。

资深的DFT工程师(5年经验)基本月薪就能拿到50-80K,当前IC设计行业正处于飞速发展的风口之下,DFT作为把控芯片质量的必要岗位,企业对DFT人才的需求可谓是日益旺盛。所以对于即将走入IC设计行业的科班人,亦或是其他专业有意转行IC的在职人,DFT将是你踏入IC行业一个不错的选择。

就业薪资(参考):

平均薪资36W/年

初级工程师(20W-50W)、中级工程师(45W-80W)、高级工程师(60w-100w)

适用人群:

有意应聘DFT设计工程师的在职人员(本科及以上学历);

电子类在校研究生(含材料、工艺、物理、自动化等专业);

职业简介:

1.将DFT技术,常见的如Scan,Mbist,Boundary Scan技术,实现到设计中去

2.产生测试向量并验证测试向量

3.协助后端实现工程师完成test模式的时序收敛

4.协助测试工程师进行机台调试,debug 测试failure,提高芯片良率

工作内容:

1.参与芯片DFT架构定义和设计

2.完成DFT电路设计,包括Scan、Mbist、Bscan等

3.协助后端团队处理DFT相关的时序分析和timing收敛工作

4.使用EDA工具生成测试向量,并且进行仿真验证

5.参与ATE,debug 测试failure