打造IC人才

科技生态圈

打造IC人才

科技生态圈

发布时间:2023-01-16

来源:IC修真院

Verilog HDL与VHDL是当前最流行的两种硬件设计语言,两者各有优劣,也各有相当多的拥护者,都通过了IEEE 标准。VHDL在北美及欧洲应用很普遍,Verilog HDL 语言在中国、日本、韩国、美国等区域应用很普遍。本文简要地介绍国内数字电路设计普遍使用的Verilog语言。

1、verilog是什么?

Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式等数字逻辑功能。

特点:

verilog很多操作符和结构类似与C语言,比如算术运算符、条件语句、循环语句等,易学易用。

内置各种基本逻辑门,便于进行门级机构描述;内置各种开关级软件,可进行开关级建模。

既适合可综合的电路设计,也可胜任电路与系统的验证。

能从多层次(开关级、门级、寄存器传输级、行为级)对设计系统进行描述。

灵活多样的电路描述风格,支持混合建模。

2、电路描述示例

示例1:

图左边是与门电路符号,右边是把左边电路转换成verilog描述。

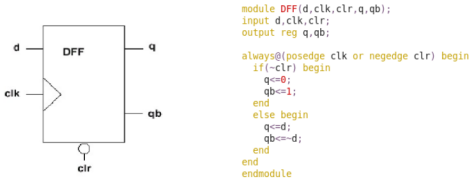

示例2:

图左边是异步复位触发器电路,右边是把触发器电路转换成verilog描述。

3、基本语法介绍

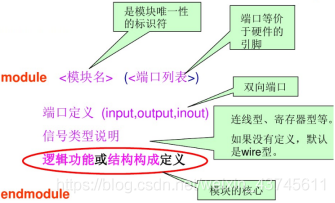

Verilog语言采用模块化设计,以模块集合的形式来描述数字系统。模块(module)可以理解为verilog HDL语言的基本描述单位,它用于描述某个电路的功能或结构,以及该模块和其他模块通信的输入输出端口。模块支持层次嵌套,一个模块可由若干子模块构成,模块所构建的硬件电路可以是基本门电路也可以是一个复杂的系统电路。

模块的结构如下图所示。每个模块必须以module开头,以endmodule结尾;设计模块还需要定义端口,用input、output、inout分别描述输入、输出、双向端口;模块中间的Verilog程序的书写类似C语言,每条语句以分号结束;使用“/…/”和“//”可以对多行或一行程序进行注释。

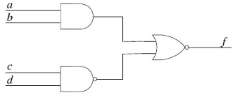

①用assign描述持续赋值

assign语句一般用于组合逻辑电路赋值,也称之持续赋值,例如下图电路结构可描述为:

assign f=((a&b)|((c&d)));

②用always描述过程块赋值

例:16位的计数器模块设计

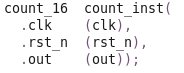

③模块实例化(调用模块)

Verilog中一个模块调用另一个模块是通过实例化来实现的,这样就能建立起层次化的设计结构。

例如在其他模块调用上面的16位计数器模块。

市场上verilog书籍非常多,建议选择一本较为经典教程通读,国内夏宇闻老师的《Verilog数字系统设计教程》 作为入门教程就很多错。

相关推荐:

上一篇:数字ic设计教程-初识FPGA

推荐阅读

2023-04-24

2023-03-22

2022-11-23

2022-12-26

2022-12-28