打造IC人才

科技生态圈

打造IC人才

科技生态圈

发布时间:2023-01-16

来源:IC修真院

1、什么识FPGA?

FPGA(Field Programmable Gate Array,现场可编程逻辑门阵列)是一种可编程的逻辑列阵芯片,为半定制集成电路芯片。fpga是一种用户可自行定义结构和功能的电子器件,它拥有72变的本领,可重复烧录,用户根据功能需求编写程序生产bit流文件并烧录到芯片内就可实现预期的数字电路功能。

FPGA相对与ASIC优势:

(1)FPGA实现比ASIC设计周期短。基于FPGA的设计流程比ASIC简单很多,无需人工参加布局布线,没有掩模和其他制造步骤。

(2)FPGA比ASIC开发成本低(批量生产的ASIC单位成本一般比FPGA低):ASIC的NRE(Non-recurring engineering,一次性工程费用)费用非常高,万一流片的IC失败,必须耗巨资重新设计。ASIC开发的EDA工具、IP、人力、流片、封装等成本都很大,所以FPGA的开发成本与ASIC相比不可同日而语。

(3)FPGA比ASIC设计灵活:因为FPGA易于修改,可重复编程,所以FPGA设计迭代速度很快,可加速新产品上市进程。

可以说,FPGA芯片是小批量品产提高系统集成度、可靠性的最佳选择之一。由于FPGA具有布线资源丰富,可重复编程和集成度高,投资较低的特点,在IC原型验证、通信设备、数字信号处理、汽车电子、军事、航空、SOPC、数据采集、逻辑接口控制等领域有广泛的应用。

从玩单片机转到玩FPGA的同学可能会困惑在两者区别上,最大的区别就在于:FPGA设计的是数字电路,单片机设计的是软件程序。下图来一张FPGA开发板图片。

3、FPGA结构

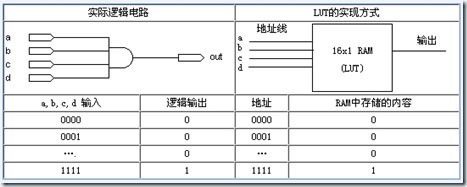

FPGA 的基本结构包括可编程I/O(输入输出单元),可编程逻辑单元,数字时钟管理模块,嵌入式块RAM,布线资源,内嵌专用硬核,底层内嵌功能单元等资源。学习过数字电路的同学知道与或非门可以构成几乎所有的数字电路,但是FPGA内部的基本单元并不是与或非门,而是由无数LUT(Look Up Tabe,查找表)和寄存器构成。以下图4输入的LUT为例看看其原理,4输入的LUT实际上是4位地址线连接到深度为16位宽为1的存储器,能够存储16位数据,所以在FPGA设计中可以用LUT组建分布式的RAM。

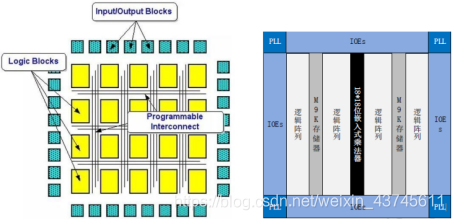

下图左边部分是一个基本的FPGA组成模块图,右边部分是某款FPGA的结构图(不同型号芯片结构都有差异)。

资源介绍:

①可编程逻辑块(Logic Block)

Xilinx公司称之为可配置逻辑块(CLB),其基本逻辑单元称之为Slice(切片); Altera公司称之为逻辑阵列块(LAB),其基本逻辑单元是LE(Logic Element)。多个基本逻辑单元通常规则地排成一个阵列结构,分布于整个芯片;

②可编程互连资源

包括各种长度的连线线段和一些可编程连接开关,它们将各个可编程逻辑块或输入/输出块连接起来,构成特定功能的电路。用户可以通过编程决定每个单元的功能以及它们的互连关系,从而实现所需的逻辑功能。

③可编程I/O(输入/输出)

完成芯片内部逻辑与外部管脚之间的接口,围绕在逻辑单元阵列四周。

④锁相环(PLL)

模拟电路,将输入的周期信号进行分频和倍频,以及相位、占空比调制。输出一个或多个稳定的时钟信号,并连接到全局时钟网络上,以保证时钟的质量,减小时钟偏斜(Skew)和抖动(Jitter)。

⑤存储器

嵌入式块RAM,这些存储器可以被配置不同类型RAM、ROM、FIFO、移位寄存器等,在存储数据或跨时钟数据传输时常用到。相对于LUT构成的分布式RAM(Distribute RAM),片内自带存储单元容量更大,从而避免LUT资源的浪费。

⑥乘法器

嵌入式乘法器(也称DSP块):该单元可快速进行数学运算,如实现有限冲激响应滤波器(FIR),无限冲击响应滤波器(IIR),快速傅里叶变换(FFT),离散余弦变换(DCT)等时会消耗很多逻辑资源,这时候使用嵌入式乘法单元这就不会浪费有限的LUT和寄存器资源。

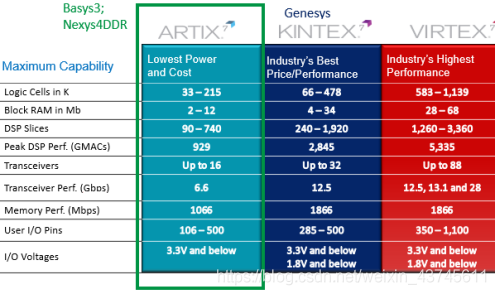

下面看看Xilinx 7 系列FPGA的资源情况。

3、FPGA在IC验证中的应用

基于FPGA的原型设计已是一种成熟的技术,它可以代表一个近乎精确的以高速运行的设计复制品。这种复制品可用于功能逻辑验证、软件验证、硬件/软件协同验证,可用于现场测试等方面。现在FPGA的制造工已越来越先进,片内可用资源越来越多,配套软件的功能愈发强大,这使FPGA原型设计变得更加简单和强大。

芯片在制造出来之前,在RTL代码验证上需要花费很多时间,随着芯片性能的提高、集成的IP越来越多,SOC系统愈发复杂,这给芯片验证带来了资金和时间上的挑战。FPGA相对于软件仿真器(VCS、NC等仿真工具)更接近真实芯片,运行速度大幅度提升(仿真器上跑一天的激励在FGPA可能几分钟就跑完),FPGA相对于硬件仿真加速器(Cadence的Palladium,Synopsys的ZeBu,Mentor的Veloce)有巨大的成本优势。利用FPGA可以进行RTL验证、加速仿真进度、提前进行相关应用研发等,所有这些因素都有助于降低设计成本并缩短上市时间,降低重新调整的风险。因此FPGA的IC原型验证在数字芯片设计中有极为重要价值。

当然FPGA原型作为芯片的替身,也有诸多限制,比如规模限制,速度限制,功耗限制,结构限制等,在使用FPGA原型作为芯片的替代时,需要进行相应的修改,才能完成相应功能,甚至有些功能最终无法覆盖。

相关推荐:

推荐阅读

2023-01-17

2022-06-27

2023-05-22

2023-06-08

2022-11-02